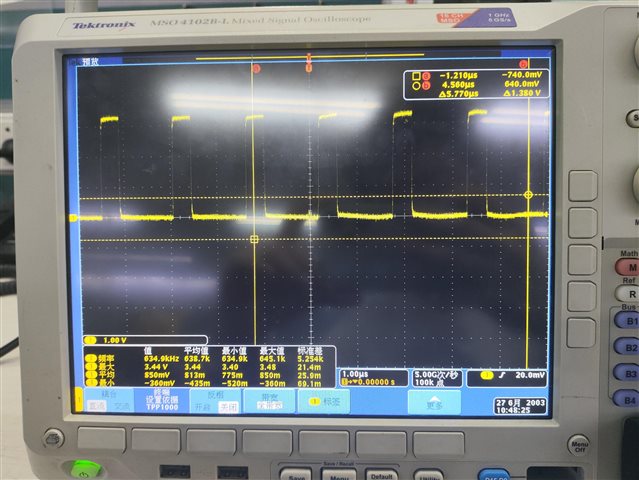

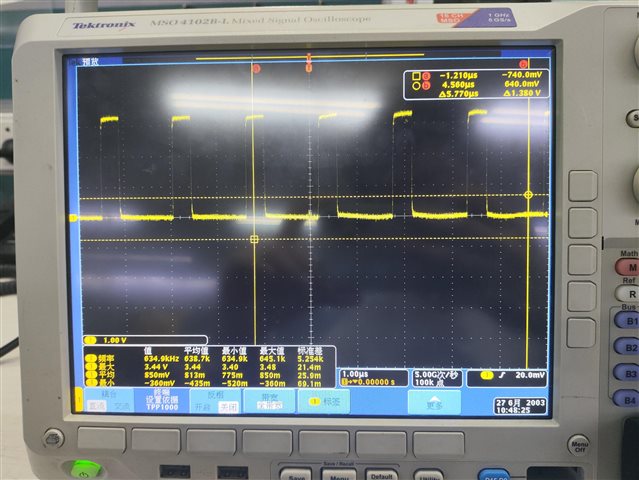

通过CDCE62005 EVM工具生成5路lvds格式输出5路128MHz的LVDS格式时钟时,LOCK引脚的信号如下,请问是什么原因?

对应的时钟配置参数图下:

REGISTERS

0 EB860320

1 EB860301

2 EB860302

3 EB860303

4 EB860314

5 10000BE5

6 04BE0126

7 BD0037F7

8 20009D98

PORTS

0 9D

1 FF

2 DF

3 F9

INPUTS

PRI 40

SEC 0

AUX 25

EXTERNAL COMPONENTS

C4 129.8245

R4 61.9546m

C5 684.4536m

注:在使用CDCE62005 EVM工具配置5路LVDS 100MHz和200MHz输出时,LOCK信号能正常拉高,在测试5路128MHz和150MHz时出现上述问题。