Part Number: LMK04832

为了优化相噪,LMK04832配置时钟输出时,IDL和ODL的配置一般怎么考虑,有没有统一的做法?还是说根据所研发产品的实际情况去调试,由调试结果决定是开启还是关闭改配置?

比如245.76MHz需要优化相噪一般是否开启IDL和ODL,2949.12MHz一般怎么配置IDL和ODL。如果同一颗芯片中,245.76MHz开启了IDL和ODL,那么是否有可能对2949.12MHz的时钟产生更严重的干扰。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

为了优化相噪,LMK04832配置时钟输出时,IDL和ODL的配置一般怎么考虑,有没有统一的做法?还是说根据所研发产品的实际情况去调试,由调试结果决定是开启还是关闭改配置?

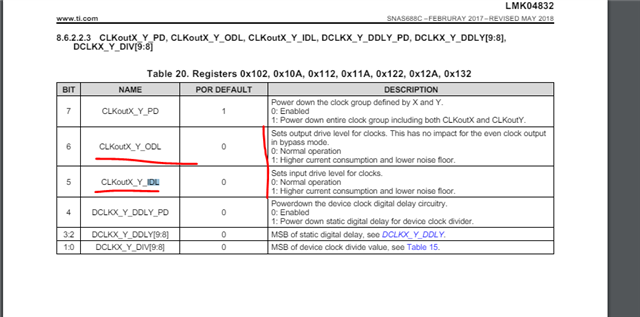

根据datasheet说明,您根据您的实际情况来配置。

比如245.76MHz需要优化相噪一般是否开启IDL和ODL,2949.12MHz一般怎么配置IDL和ODL。如果同一颗芯片中,245.76MHz开启了IDL和ODL,那么是否有可能对2949.12MHz的时钟产生更严重的干扰。

官方有相关示例说明请参考以下官方说明原文

In this example, the 245.76-MHz ADC output needs the best performance. CLKout2 on the LMK04832 provides the best noise floor / performance. The 245.76 MHz is placed on CLKout2 with 10.24-MHz SYSREF on CLKout3. • For best performance the input and output drive level bits may be set. Best noise floor performance is achieved with CLKout2_3_IDL = 1 and CLKout2_3_ODL = 1. • The CLKoutX_Y_ODL bit has no impact on even clock outputs in high performance bypass mode

如第一个问题和示例说明,您如果根据实际情况有具体要求,您可以对照第一个问题表格,参考例子中的说明来配置。