Part Number: LMK04828

您好TI工程师,我最近在调试我们的一款时钟芯片04828,但是对芯片的相关进行配置后发现PPL1和PPL2均无法锁定

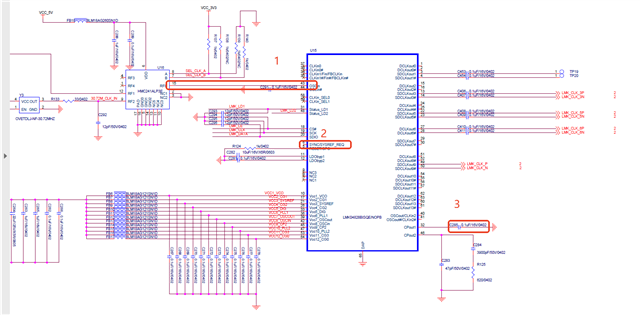

硬件电路图:

1、在硬件上尝试做了下面修改采用FREF_RX_IN 输入10Mhz时钟。

2、增加了SYNC/SYSREF_REQ控制信号,使用控制芯片在完成配置后设置为高电平后写寄存器0x0144 0XFF

3、去掉了CPout1的电容使其悬空。

软件配置:

寄存器文件如下:

R0 (INIT) 0x000090 R0 0x000000 R2 0x000200 R3 0x000306 R4 0x000438 R5 0x000503 R6 0x000601 R12 0x000C51 R13 0x000D08 R256 0x010014 R257 0x010100 R258 0x010200 R259 0x010300 R260 0x010420 R261 0x010500 R262 0x0106B0 R263 0x010777 R264 0x010814 R265 0x010900 R266 0x010A00 R267 0x010B00 R268 0x010C20 R269 0x010D00 R270 0x010EB8 R271 0x010F00 R272 0x011014 R273 0x011100 R274 0x011200 R275 0x011300 R276 0x011400 R277 0x011500 R278 0x0116B8 R279 0x011700 R280 0x011814 R281 0x011900 R282 0x011A00 R283 0x011B00 R284 0x011C00 R285 0x011D00 R286 0x011EB0 R287 0x011F70 R288 0x012014 R289 0x012100 R290 0x012200 R291 0x012300 R292 0x012408 R293 0x012500 R294 0x0126B0 R295 0x012770 R296 0x012814 R297 0x012925 R298 0x012A25 R299 0x012B20 R300 0x012C25 R301 0x012D25 R302 0x012E28 R303 0x012F11 R304 0x013014 R305 0x013100 R306 0x013200 R307 0x013300 R308 0x013420 R309 0x013500 R310 0x0136B0 R311 0x013711 R312 0x013805 R313 0x013903 R314 0x013A02 R315 0x013B80 R316 0x013C00 R317 0x013D00 R318 0x013E00 R319 0x013F00 R320 0x014003 R321 0x014100 R322 0x014240 R323 0x014311 R324 0x0144FF R325 0x014500 R326 0x014608 R327 0x01471A R328 0x014802 R329 0x014902 R330 0x014A00 R331 0x014B00 R332 0x014C00 R333 0x014D00 R334 0x014E00 R335 0x014F00 R336 0x015000 R337 0x015103 R338 0x015200 R339 0x015300 R340 0x015478 R341 0x015500 R342 0x015678 R343 0x015700 R344 0x015896 R345 0x015900 R346 0x015A0A R347 0x015BD4 R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F3B R352 0x016000 R353 0x016119 R354 0x016245 R355 0x016300 R356 0x016400 R357 0x01650B R369 0x0171AA R370 0x017202 R380 0x017C15 R381 0x017D33 R358 0x016600 R359 0x016706 R360 0x016800 R361 0x016959 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E1B R371 0x017300 R386 0x018200 R387 0x018300 R388 0x018400 R389 0x018500 R392 0x018800 R393 0x018900 R394 0x018A00 R395 0x018B00 R8189 0x1FFD00 R8190 0x1FFE00 R8191 0x1FFF53

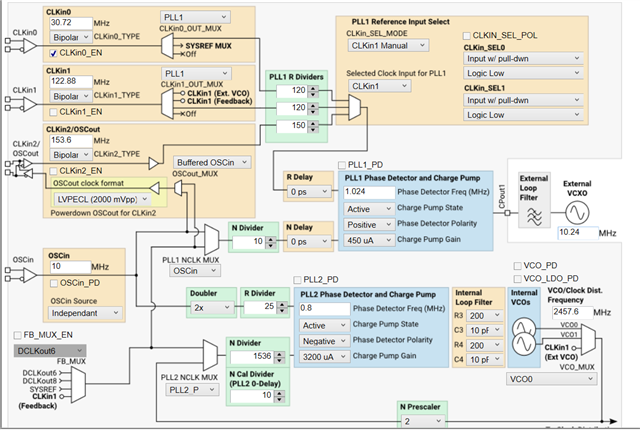

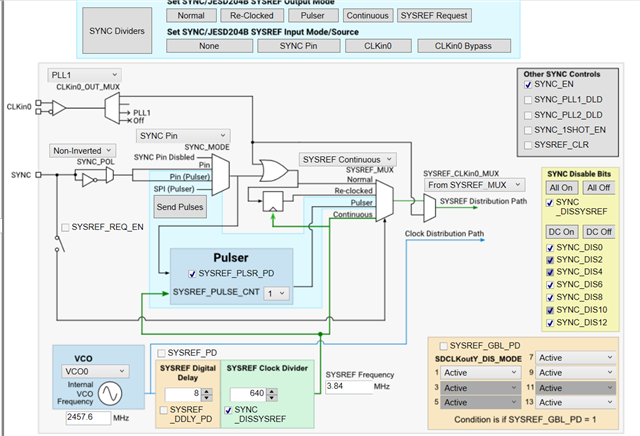

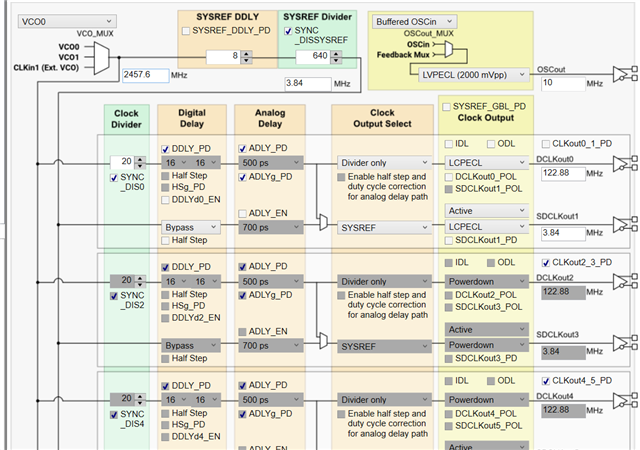

软件配置界面如下:

整体的配置如上所示,还麻烦TI工程师帮我看看问题所在,以及如何解决当前无时钟输出的问题。