Part Number: LMK04828

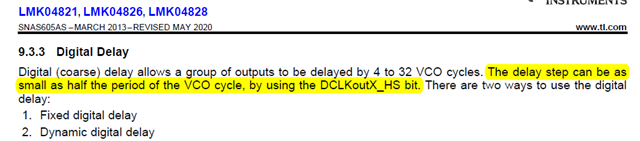

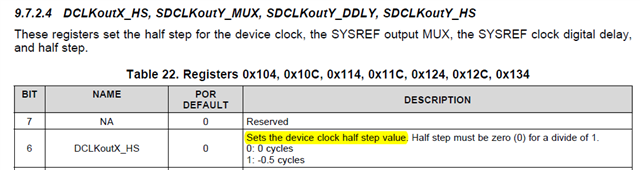

芯片为LMK04828,VCO频率为2.5GHz,周期为400ps,半周期即为200ps。若设置DCLKoutX_HS = 1,指的是DCLKoutX输出时钟信号偏移0.5个VCO周期,还是说:DCLKoutX_DDLY_CNTH/L的延迟步进或单位等于1/2 VCO周期?

比如DCLKout2 = DCLKout4 = 250MHz(周期4ns),要想两个时钟的相位差为200ps,如下步骤可否实现?

(1)DCLKout2_HS = DCLKout4_HS = 1;

(2)DCLKout2_DDLY_CNTH = 0xAA;DCLKout4_DDLY_CNTH = 0xAB;两者偏差一个步进即200ps;