Part Number: LMX2582

我们的项目中有用LMX2582锁相环芯片,锁相环的输入(refclk)为10MHz,输出为5237.76MHz。LMX2582及其外围电路如附件中所示:

LMX2582_CLKP/N为锁相环参考输入,频率10MHz;

AD9163_RFoutAP_R/AD9163_RFoutAM_R为锁相环的其中一路输出,频率为5237.76MHz;

LMX2582_RFoutAP_R/LMX2582_RFoutAM_R为锁相环的另一路输出,频率也为

5237.76MHz;

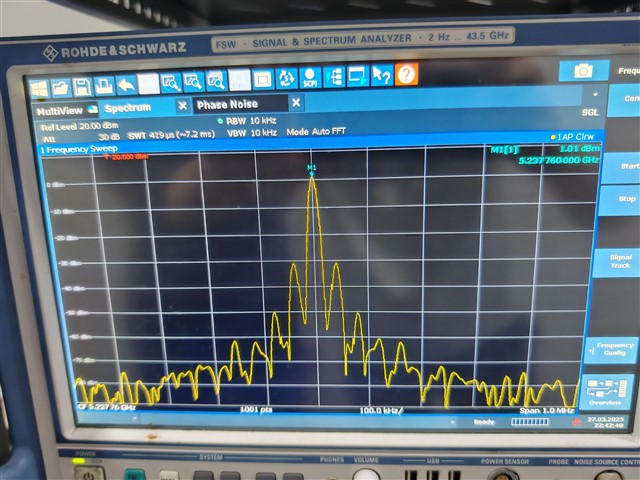

我们用频谱仪测量时钟的质量时,结果如下:

频谱测量结果显示相噪比较大,怀疑LMX2582的VCO环路补偿值我们设置的不对。所以想请你们帮忙看一下我们环路补偿的阻容值是否可以优化。

提前表示感谢!