Part Number: LMK04821

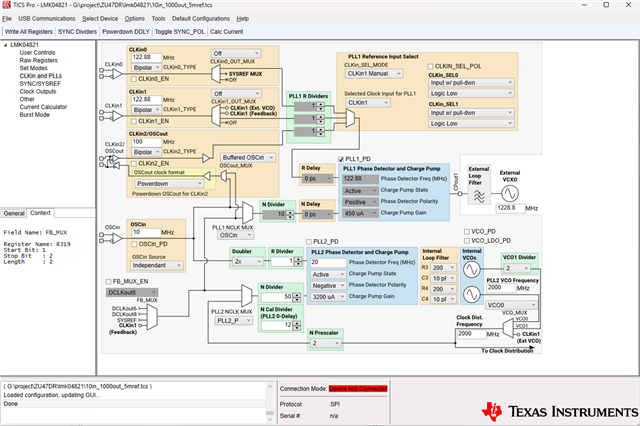

外部硬件设计OSCin输入10M,PLL2无法锁定,具体参数设计及外部环路滤波如图,请熟悉该问题或此芯片应用的工程师帮忙解答或提供思路,期待您的回复

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您的10MHz 是正弦波吗? 正弦波最大压摆率为2π* f * Vpk、对于3.3Vpp 10MHz、正弦波低于所需的最小输入压摆率0.15V/ns。 在10MHz 处、需要削波正弦波或方波(LVDS、LVPECL 等)。

确保您也将 PLL2_N_CAL (位于 PLL2_N 下方)设置为50。 这是 VCO 校准正常工作所必需的。

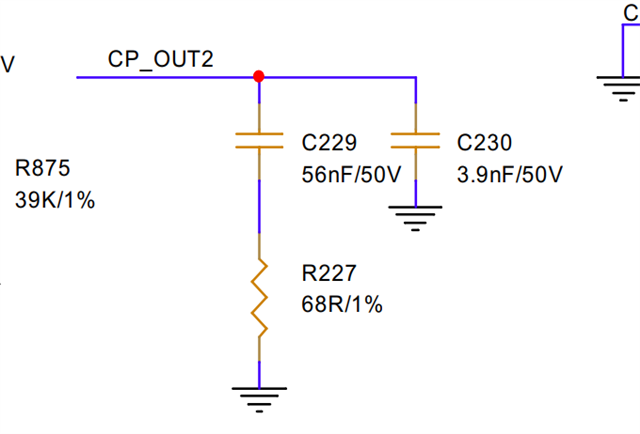

如果我正确读取了环路滤波器中的电阻(68Ω)、环路滤波器不是很稳定。 尝试使用680Ω(而不是68Ω)之类的器件。 使用680Ω 时、带宽为43kHz、相位裕度为50°;使用68Ω 时、带宽为15kHz、相位裕度为18°。 我已经附加了显示以下差异的 PLLatinum Sim 文件-检查中间或高级功能级别以查看相位噪声图并粗略估算稳定性。