Other Parts Discussed in Thread: LMK04826, LMK04828

LMK04821能否和LMK04826/8直接兼容,外围电路是否需要修改?除了VCO输出频率不同,还有什么其他重要差异?目前希望应用于WiFi设备,VCO频率需要为320M的整数倍。

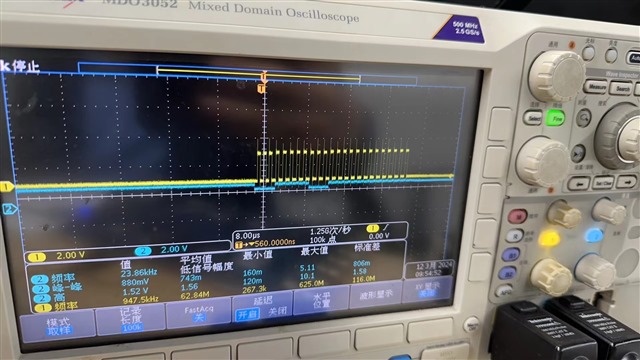

芯片供电3.3V正常。测量SPI波形异常,无法写入及读取。FPGA端发送波形正常,经过串联电阻22欧姆与芯片相连(或与芯片直连)后,波形发生变化,时钟幅值到不了3.3V 只有2V左右。

FPGA与LMK04821之间只有电阻连接,未经过其它器件。

LMK04821由FPGA进行驱动控制,正常电路如图所示,调试过程发现SPI接口的CSn无法正常拉高,将CSn上的串接电阻改为1K,串接电阻距离LMK04821器件管脚只有1cm,且FPGA和LMK04821在同一个PCB板卡上…

在通过SPI配置LMK04821时,发现SDIO的管脚不能正常的拉高或者拉低,导致MCU与LMK04821通信失败,SDIO的幅值一直在1.5V左右。请教一下如何处理。SDIO管脚外部上拉4.7K

地址1f1f 数据ff

在调试过程中,发现OSCIN没有时钟输入的时候,LMK04821依然有时钟输出,这个现象正常吗?恢复250M的时钟后,JESD204B出现建链异常的问题。

主要的疑虑是:为什么没有时钟输入的时候,LMK04821仍然有频率输出?会有轻微频偏。

正常输入250MHz时钟后,jesd204B通信反而出现问题?

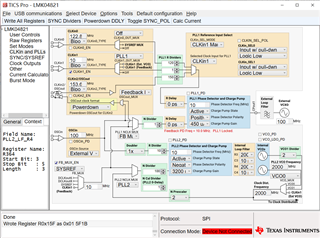

我们使用LMK04821芯片的单PLL模式,从OSCin输入125Mhz的差分时钟,配置参数如下。

测试中发现,输出的时钟频率基本上是对的,但PLL2不能lock。

请问可能是什么原因?需要如何调查和解决这个问题?谢谢!

LMK04821问题:

1、两级锁相环的分频器输出波形占空比不是50%,基本为(n-1):1;

2、PLL1无法锁定;

3、PLL2在特定鉴相频率下能锁定;

4、拉SYNC管脚对齐device clock,不生效;

我这边使用lmk04821,工作在Dual-pll cascaded zero-delay mode, TICS pro配置文件为lmk04821_config.tcs,参考时钟输入为10MHz、5dBm正弦波,从CLKin1输入。通过FPGA抓取芯片IO输出的PLL_DLD信号。发现PLL1偶尔会失锁,失锁后大约0.16ms再锁定;PLL2始终锁定。请问PLL1失锁的原因可能是什么,是否是配置不对。

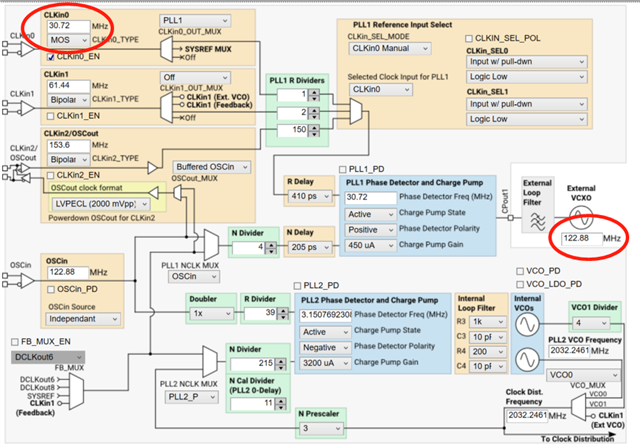

用CLKIN0 作输入,输入为61.44MHZ 时,LOCK灯是亮,把频率改为30.72MHZ,同步修改RDIVIDER 值,为什么无法锁定,对CLKIN0 的频率有严格要求吗

另外:PLL2的锁定和输出频率与PLL1的锁定与否没关系是吗,CLKIN0的输入频率并不影响板上EXTVCO的运行对吗,也就是说不管CLKIN0频率多少或者是否稳定,EXTVCO 都是正常运行的,对吧

配置参数

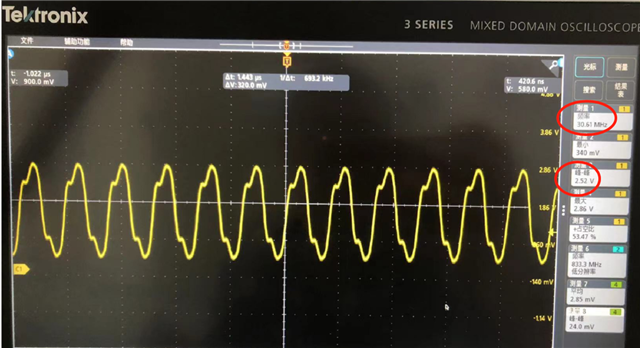

输入时钟波形

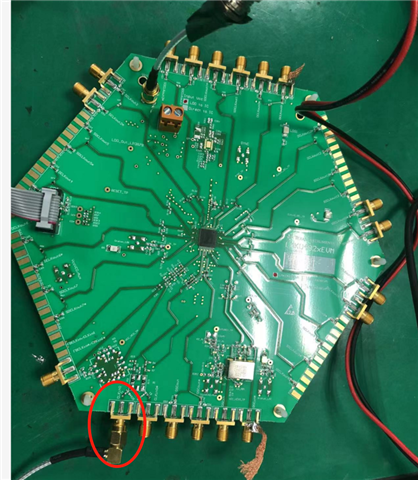

评估板

我现在想读取LMK04821寄存器的值,比如说我配置了0x001为0x90,可以查询到0x000的值吗?需要切换什么寄存器的状态才可以吗?

我希望的是去读取寄存器的状态来保证我是否配置成功,然后也需要查询那几个只读寄存器,像0x003 0x006 ,我从技术那边了解到了:读寄存器让R/W为1就可以,但是我这样试了之后并没有返回值给我

我需要知道的是在读寄存器的时候需要配置哪些寄存器能达到我的目的,忽略前面的配置情况,相当于重新刷新配置状态,手册里提到input…