Part Number: ADS131E08

Hi,

我们在用采购的ADS131E08 的EVM测试SNR,发现用板子上的HC735-2.048MHZ测试50hz的SNR时,可以测到107dB(datarate=8ksps)。相同的测试环境和测试点数,只是把CLK改成芯片内部CLK源后,SNR只能测到94dB,并且发现50hz信号频谱泄露严重。想请教下你们用内部时钟测试得到的SNR是多少呢?如果也测不到107dB的话,想请教下内部CLK下SNR变差的原因会是什么呢?感谢感谢~

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS131E08

Hi,

我们在用采购的ADS131E08 的EVM测试SNR,发现用板子上的HC735-2.048MHZ测试50hz的SNR时,可以测到107dB(datarate=8ksps)。相同的测试环境和测试点数,只是把CLK改成芯片内部CLK源后,SNR只能测到94dB,并且发现50hz信号频谱泄露严重。想请教下你们用内部时钟测试得到的SNR是多少呢?如果也测不到107dB的话,想请教下内部CLK下SNR变差的原因会是什么呢?感谢感谢~

EVM板上的J5/J6/J10断开后,ADS131E08 会工作在内部时钟;其他连接跟用外部时钟测试时是一样的。

J5/J6/J10?您是指JP5/JP6/JP10。我的问题是关于输入连接。你使用的输入信号幅度仅为0.5Vpp,这不是测试信噪比性能的正确信号。另请注意,数据表中的107dB规格是用外部时钟测试的。

我不知道你在测试ADC时是否将CLKSEL引脚设置为高,并将CLK_EN位设置为0。CLK引脚是主时钟输入,如果未使用,应连接到DGND。

1. ”J5/J6/J10?您是指JP5/JP6/JP10“-----是的,我回答中的J5/J6/J10指的是JP5/JP6/JP10,JP5/JP6/JP10都断开后,CLKSEL引脚接的是DVDD的3.3V,寄存器CLK_EN位是设置为0的。此时ADS131E08 会工作在内部时钟模式下

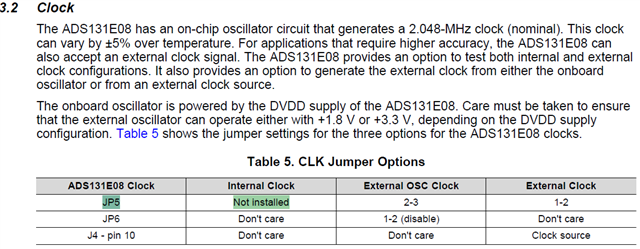

2. “CLK引脚是主时钟输入,如果未使用,应连接到DGND”------这句话我没太理解,是指用内部CLK模式时,并且不需要CLK_EN=1时,CLK引脚需要接到DGND么?但是在ADS131E08的EVM guide里面提到,用内部时钟时,JP5是not installed,如下图,这点需要请您再帮忙确认下。

3. 我在测试SNR的时候,输入的信号幅度是4.5VPP(-0.5dBFS)的正弦波信号,VCM=1.5V,VREF=2.4V,AVDD是3V,AVSS=0V。外部时钟和内部时钟测试时的CLK信号是一样的。

4. “数据表中的107dB规格是用外部时钟测试的”------是的,只是我们想知道下你们用内部时钟测试SNR的方法和测试结果,便于我们排查内部CLK SNR变差的原因是否是因为环境或者接线引起的。另外外部时钟测试的是107dB,内部时钟测试的是94dB,两者之间差异比较大,感觉不太合理,请您帮忙也确认下。

当你说4.5VPP(-0.5dBFS)时,你的信号是差分信号吗?您是否将信号连接到INxP引脚?你是如何连接INxN的?你可能违反了ADC的规范,我需要这些信息进行仔细检查。

由于本周假期,我可以在下周用内部时钟进行测试,以检查交流性能。

输入信号是差分信号,幅值是4.5VPP,将差分信号的两端接到INXP和INXN,输入信号的GND接到电路板的GND。

等待您下周测试结果,谢谢。

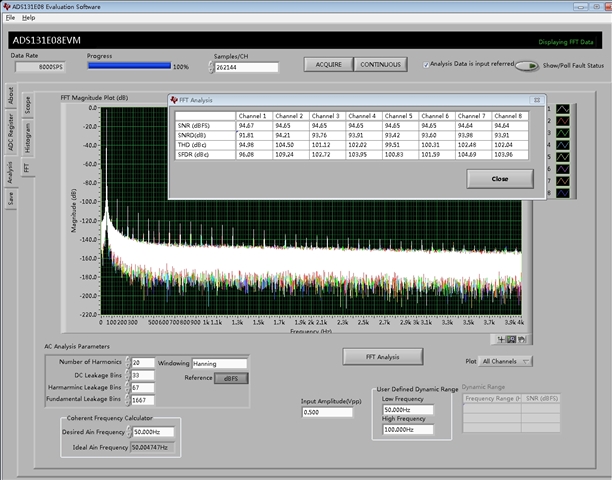

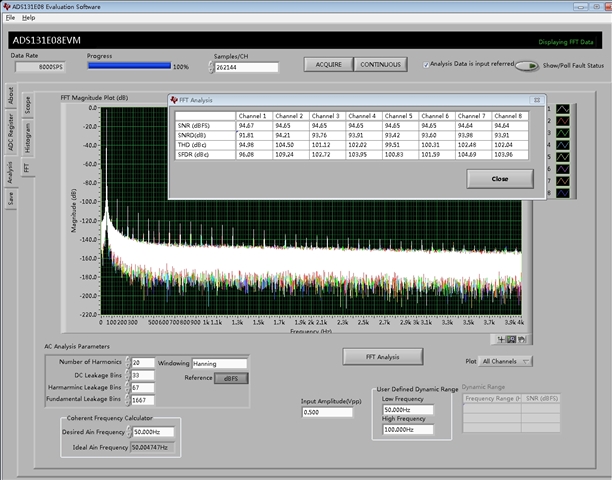

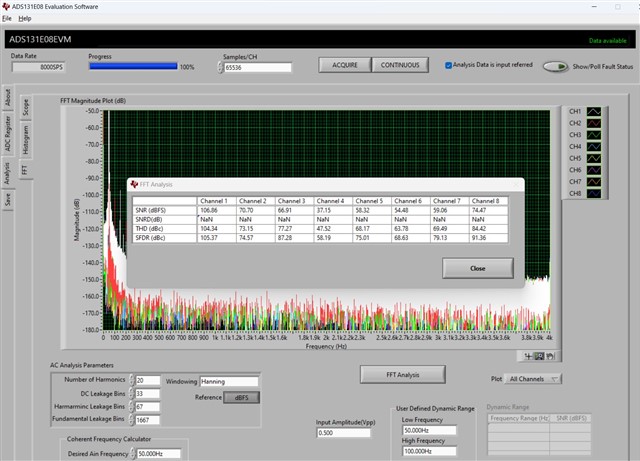

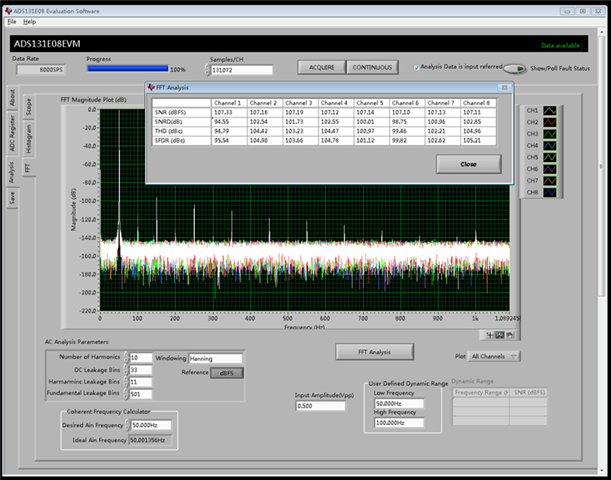

我刚根据您的配置进行了测试。我得到了一个良好且一致的结果,无论是使用外部时钟还是内部时钟。正如您在下面的图像中看到的,使用内部时钟测量的ADS131E08在我的EVM上的交流性能为106.86dB,这与我在EVM上使用外部时钟测量的接近107dB。为了在EVM上使用ADS131E08的内部时钟,您只需在EVM上进行以下配置:拔掉JP6上的跳线并保持其开放。拔掉JP10上的跳线并保持其开放,无需为JP10的中间引脚提供额外的3.3V电压,因为该信号已经通过靠近JP10的R63上拉到3.3V。对于JP5,我不确定您所说的“断开JP5”是什么意思,但跳线应从引脚2-3移到引脚1-2,JP5不应保持开放,因此我建议对EVM上的JP5进行再次检查。

感谢您的回复。我检查了J5P连接,之前JP5是断开测试的。今天将JP5接到引脚1-2测试或者将CLK引脚接到GND测试,测试结果还是94dB,跟之前的测试结果一致。

另外对您的测试结果有一些疑问,请您帮忙确认下:

1. 您的测试datarate=8k,测试点数是65536,Fundamental Leakage Bins 您设置的是1667,这样的话,会把200hz以内的谐波也包含进了信号,这个计算出来的SNR是不正确的。请您帮忙确认下

2. 下图是用外部时钟测到的SNR结果,对比内部时钟测试结果频谱泄露小很多,我们比较想知道用内部时钟频谱泄露多的原因,感谢

这实际上取决于你选择了什么样的过滤器和参数。例如, 7-term B-Harris是我们在EVM GUI软件中常用的过滤器。

7-term B-Harris是FFT分析的一种特定类型的窗口函数,您应该知道。可以为不同的应用选择不同的窗口。在这种情况下,7-term B-Harris和Hanning window的结果与我检查的结果相似。

我能够测试和验证你所看到的与外部或内部CLK的差异。内部CLK的信噪比确实比外部CLK的信信噪比差,但外部CLK的测量信噪比与数据表所示的规格相匹配,数据表说明了外部CLK的SNR/THD。