Part Number: ADS1262

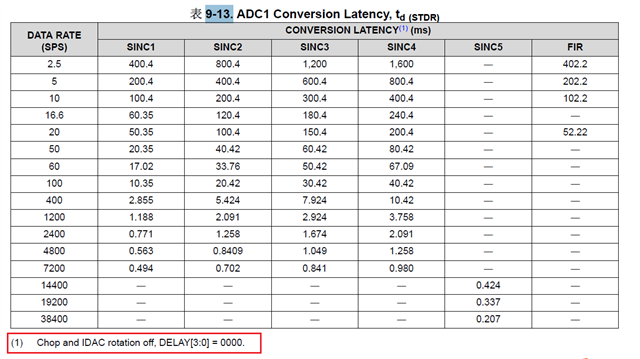

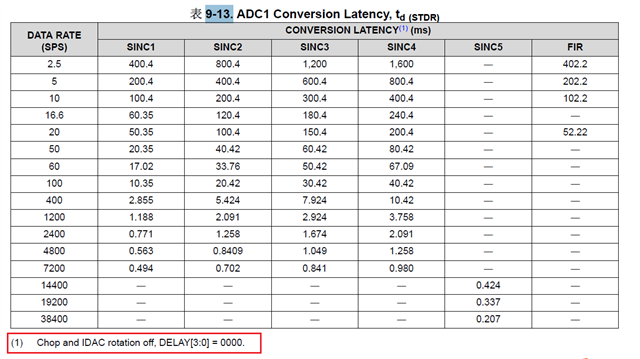

实际测试发现,在Chop Mode使能时,延迟数据与表9-13 ADC1 Conversion Latency转换延迟的数据基本一致;但是表下方的备注是Chop Mode关闭,请问为什么?

DR数据速率的所有配置都是在Chop Mode关闭下才会符合预期速率吗?比如配置SINC4, 10SPS,即每100ms输出一次采样值,Chop Mode关闭下实测是符合的,但Chop Mode使能时,就是对应表里的400ms。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS1262

实际测试发现,在Chop Mode使能时,延迟数据与表9-13 ADC1 Conversion Latency转换延迟的数据基本一致;但是表下方的备注是Chop Mode关闭,请问为什么?

DR数据速率的所有配置都是在Chop Mode关闭下才会符合预期速率吗?比如配置SINC4, 10SPS,即每100ms输出一次采样值,Chop Mode关闭下实测是符合的,但Chop Mode使能时,就是对应表里的400ms。

请参考下面链接

https://www.ti.com/lit/an/sbaa535a/sbaa535a.pdf?ts=1754314712168

Specifically section 5.6 on "Chopping"