Part Number: ADS8861

Other Parts Discussed in Thread: ADS8920B

TI专家好:

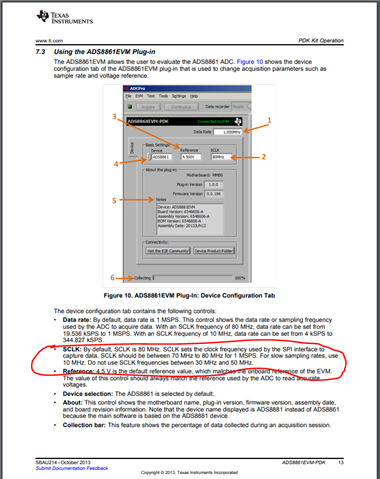

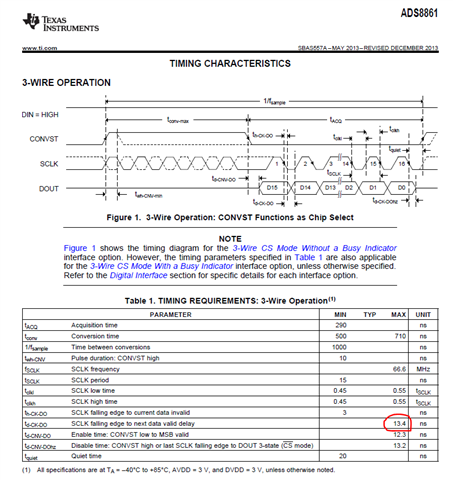

我当前的一个产品设计中选用了ADS8861这颗ADC,设计目标是实现1MSPS的最高采样率,ADC的SPI控制器基于Xilinx Spartan-6 FPGA设计。在阅读ADS8861数据手册时,发现SDO的输出延迟参数t_d-CK-DO的最大值为13.4ns,如下图所示:

依据ADS8861的t_CONV = 710ns max.,t_QUIET = 20ns min.,我计算所得的最小SCK时钟周期 t_SCLK = (1000 - 710 - 20)/16 = 16.875ns,则SPI主机的SCK输出到SDO输入(含PCB走线)的环路延迟只允许:16.875ns - 13.4ns = 3.475ns,这对于大多数基于FPGA的设计而言,基本不现实!所以我的疑问是:ADS8861数据手册中13.4ns的t_d-CK-DO数据是否过于保守?