Other Parts Discussed in Thread: ADS7853

Hi, Experts,

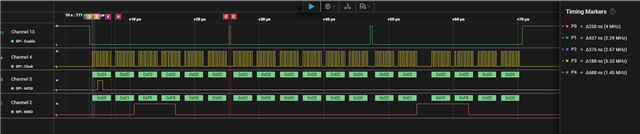

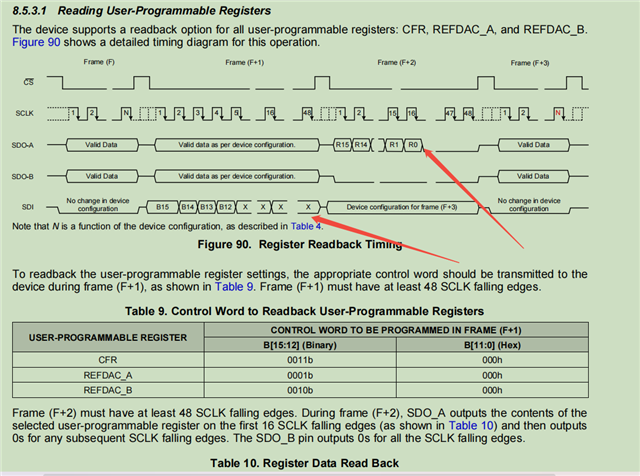

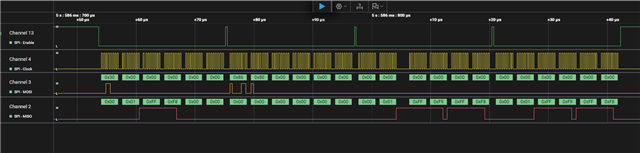

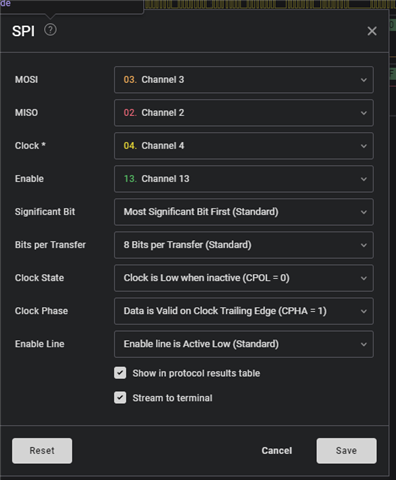

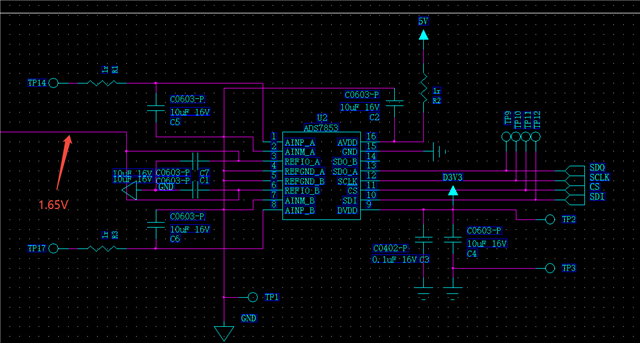

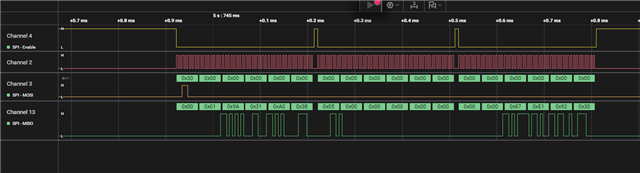

I have a problem with the communication process. When I communicate with ADS7853 using SPI, I am unable to read data correctly form the CFR register, and there are exceptions during setup. The document states that during frame (F+2), SDO-A will return the configuration value of the CFR register. Reality, there is no data return. What is happening? Moreover, after modifying the CFR register again, there was no change in re reading the register. Has anyone experienced the same problem as me.How should we solve it.

............