Part Number: DAC12DL3200

Hi,

We are working on DAC12DL3200 Digital to analog converter(DAC) with LVDS Interface operating with Single channel, 4 LVDS buses(MODE2).

We set DACCLK 4.8G, LVDS CLK 600M, and SYSREF 5M. The STROBE is set every 4 periods of LVDS CLK.

We have encountered some problems and would like to seek assistance:

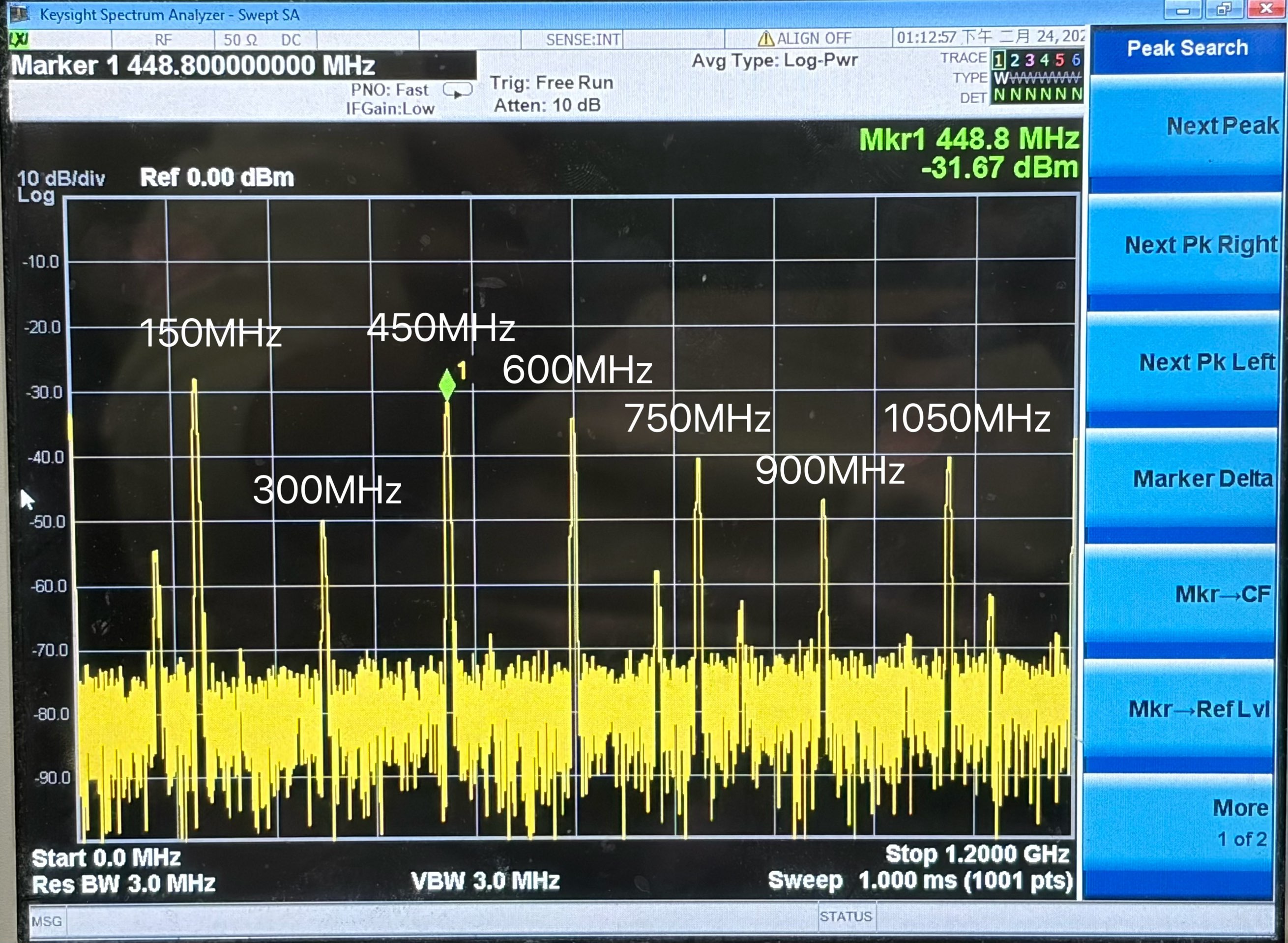

1.In addition to outputting the signals we expected, this chip also generated interference signals at frequencies such as 150M, 300M and 450M, all of which are multiples of 150M.

2. After observing the above interference signal, we no longer provide data to the chip, but the interference signal still exists.

3. We examined the registers and found: LVDS_ALM Register(0X821) always be ff (no matter STROBE is given or not); FIFO_ALM Register(0x820) always be 00.

Our registry configuration and sequence are as follows:

X”0000B0” Assert Reset

X”000200” Device Config

X”010142” CH_CFG

X”004800” DCM_EN

X”016000” MXMODE

X”002102” TXEN_SEL

X”010600” LVDS_CFG

X”090001” FUSE_STATUS(READ)

X”010001” Enable DP_EN

X”0821FF” Clear LVDS_CLK_ALM & STROBE_ALM

X”008110” Set SYSREF_RECV_SLEEP=0, SYSREF_POS_SEL=0, and SYSREF_ZOOM=1

X”008280” Set SYSREF_PROC_EN=1

X”008114” Set SYSREF_SEL

X”022001” Set SYSREF_ALIGN_EN

X”0800F1” SYNC_STATUS(READ)

X”020008” Set FIFO_DLY

X”082207” Clear All Sys_alm

Wait for 100 DACCLK cycles

X”002202” Enable TXB

Why did this situation occur? Could you please help us solve these problems?