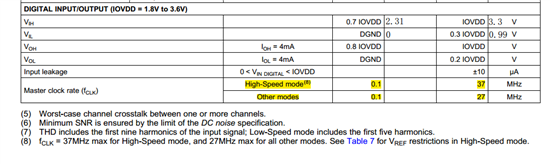

1、如果我的IOVDD是3.3V,那么我的时钟输入需要在什么电平范围呢?

datasheet上没有特别说明时钟的高低电平范围,只有数字输入/输出的电平范围。我不知道是否二者是否一样的。

2、27MHZ时钟方案。我打算使用温补有源晶振,现在发现该晶振输出波形在0.5V~1.15V左右,需不需要加个比较器或缓冲器,改变输出电平。

如果需要,能否推荐下合适的器件?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

时钟的高低电平就是digital input的Vih和Vil啊,Vih(min)=0.7IOVDD=0.7*3.3=2.31V。Vil(max)=0.3IOVDD=0.3*3.3=0.99V。