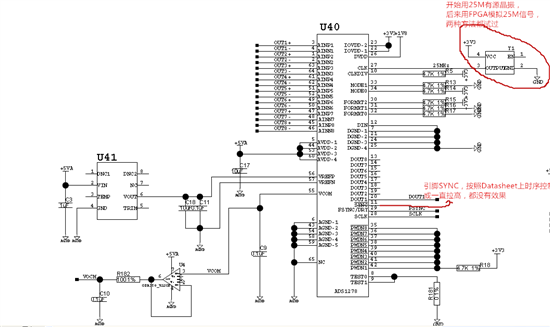

ADS1278测试板配置图在附件中,具体配置为:

High-Resolution、Frame-Sync TDM Fixed、CLKDIV=1、TEST[1:0]=0;PWDN 全部上拉到3.3V

在这种模式下,FPGA控制时序如下:

CLK=25M

SCLK=6.25M

FSYNC高电平:2个SCLK;

帧周期为2048个CLK

现象:

DOUT1端在FSYNC为高后输出第一个通道MSB数据,然后依次输出所有8个通道数据,但无论怎么改变差分输入端电压,输出端DOUT1数据始终不变,为FFFFF或00000或00001或FFFFE。个人感觉好像是ADS1278没有对输入端数据进行过采样。

如果配置成 SPI 协议模式,在DRDY变低后DOUT1端输出数据和上面描述现象一致。