我列举一下这几天的疑问,

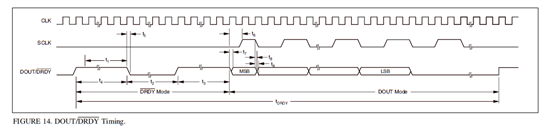

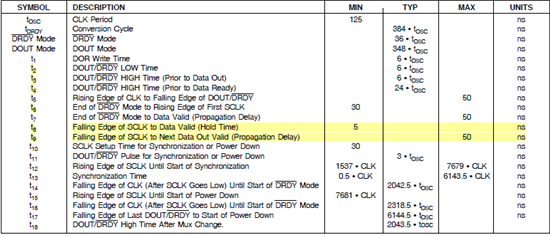

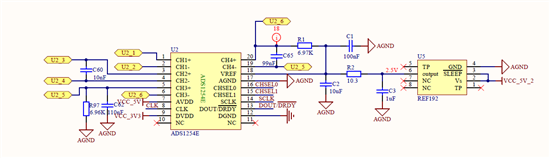

1.根据datasheet描述,The DOUT/DRDY output signal alternates between two modes of operation.AD的输出应该是在2种模式之间循环,但是经过测试发现不准确,以t4之后的下降沿为data ready依据,如果我上电之后立即检测这个下降沿,可以检测得到,但是如果我加入一个激活条件,使它在收到外部信号之后进行这个下降沿的检测,那么之后再也检测不到,换成高电平也一样,信号始终保持低电平,而不是2种模式循环,我也做过仿真,如果DRDY/DOUT能按照时序图一直变换,那么无论循环多少次,输出应该都是毫无问题的,然而实际操作时却并不是和预期一样,这是第一个问题。

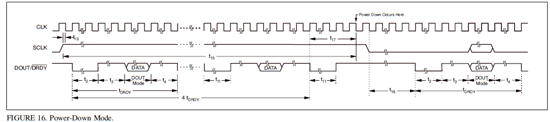

2.因为第一个问题,我想了另一个偏方来应对,上电之后将sclk拉高,足够长时间使它进入power down模式,之后收到外部信号再将sclk拉低,接下来检测下降沿,可以成功,一直到读取完24bit数据都没问题,但是关键问题来了,我想用ad实现10000个数据的连续采集,但是做完循环后测试,发现只能完成8个循环,而且异常稳定!每次都是8个循环之后无法检测到输出重新置高的时刻,突然就无法进入DRDY模式了,按理说,能进行第二次循环,那么接下来的无论多少次也没问题才对,循环部分的程序都是一样的,但是为什么后面就不行了呢?循环次数无论是10000,还是100,或者是30,结果都是在第8次循环后戛然而止,我尝试了各种方法,但是依然没有起色。

3.在尝试解决的过程中,我又有了新的疑问,先前我的clk信号是在程序中自己产生的,上电后才有,完成一次采集没有问题,但是我将clk输入换成晶振经过pll分频后的输出,却无法进行一次采集,从上电开始就无法检测到电平变换,我猜测和Prior to power-up, all digital and analog-input pins must be LOW.这个问题有关,不知道是不是?然后是DOUT的问题,24个SCLK之后是什么状态?一直保持最后一位直到下一个循环?手册上并没有提及,根据If more than 24 SCLKs were provided during DOUT mode, the DOUT/DRDY line would stay LOW until the time defined by t4.这句话,我通过提供25个SCLK,使24个SCLK之后读取下一个循环的高电平不受影响。还有这个时间表,tosc是CLK周期,那CLK也是CLK周期吧?干嘛要用两种表示方法呢,我还一度以为自己时序上出了问题。

4.然后是datasheet上我觉得有疑点的地方,The DOUT/DRDY pin is pulled LOW, indicating that new data is available to be read by the external microcontroller/microprocessor.这句话是说拉低产生的下降沿是指示标志,还是低电平是指示标志?DOUT/DRDY在我遇到问题过程中一直保持低电平,这难道是data ready?但是时序图明显又不符合,这样我最大的疑问又回到了1,ADS1254到底能不能在DRDY和DOUT两种模式之间无限循环?

以上是我的所有问题,困扰了我好几天,自己是真的解决不了了,第一次来TI论坛求助,希望大家能帮帮忙,谢谢!