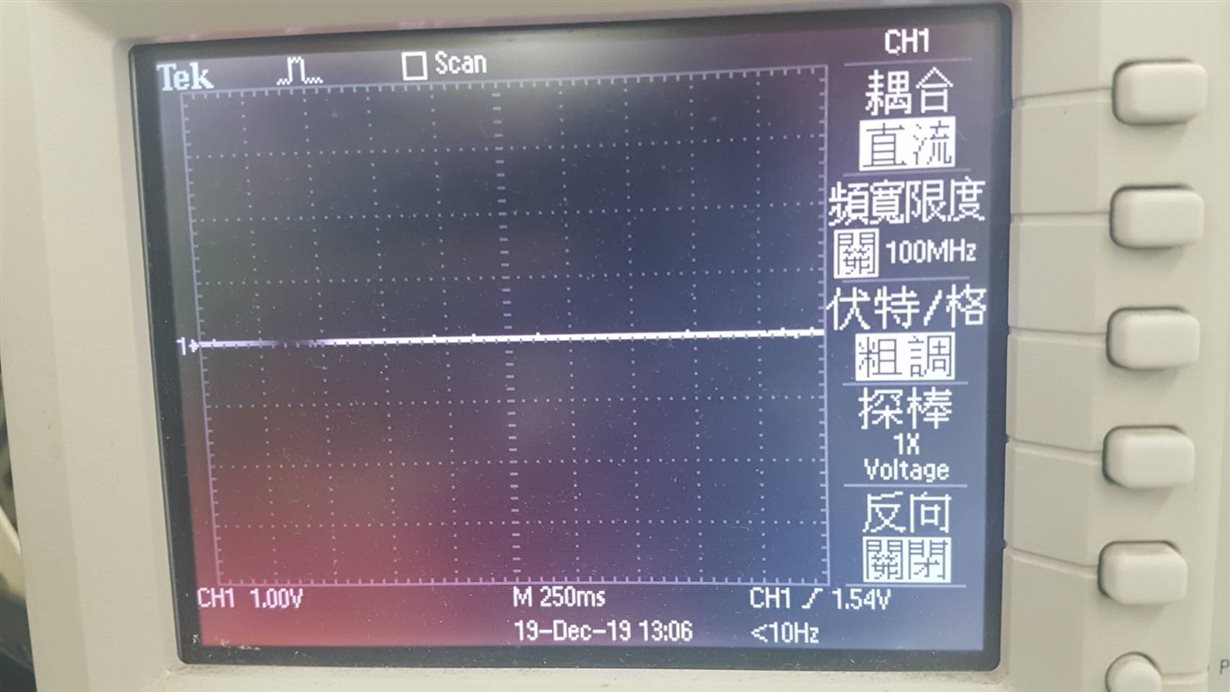

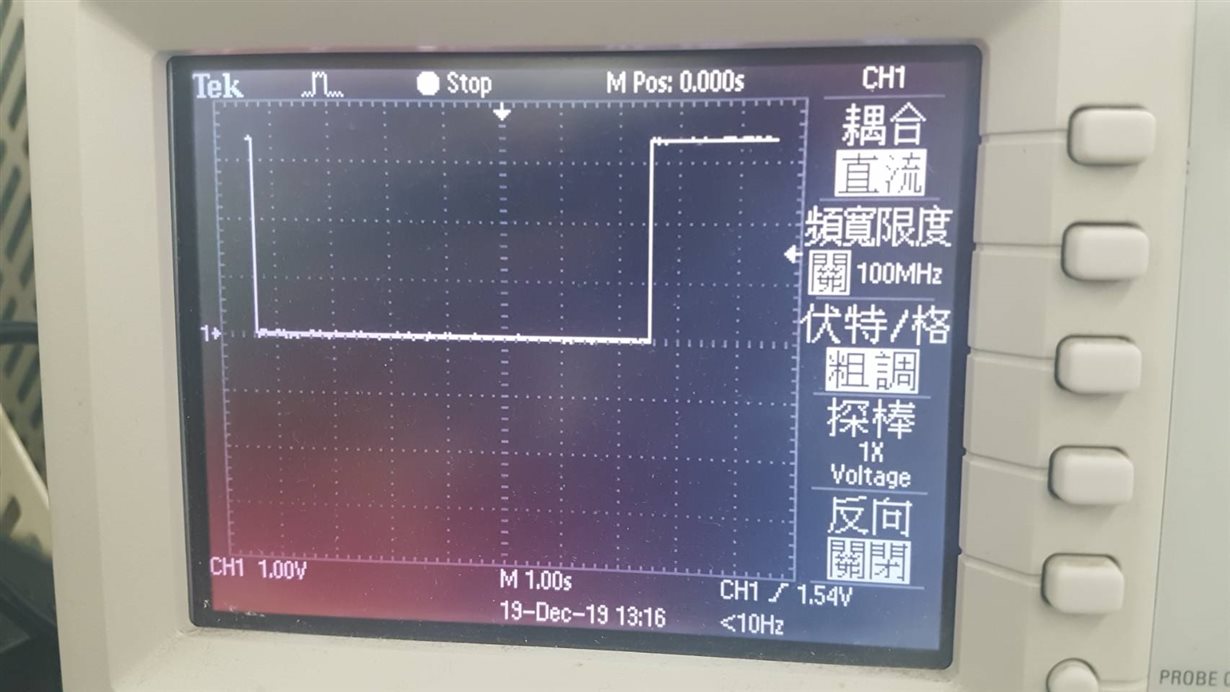

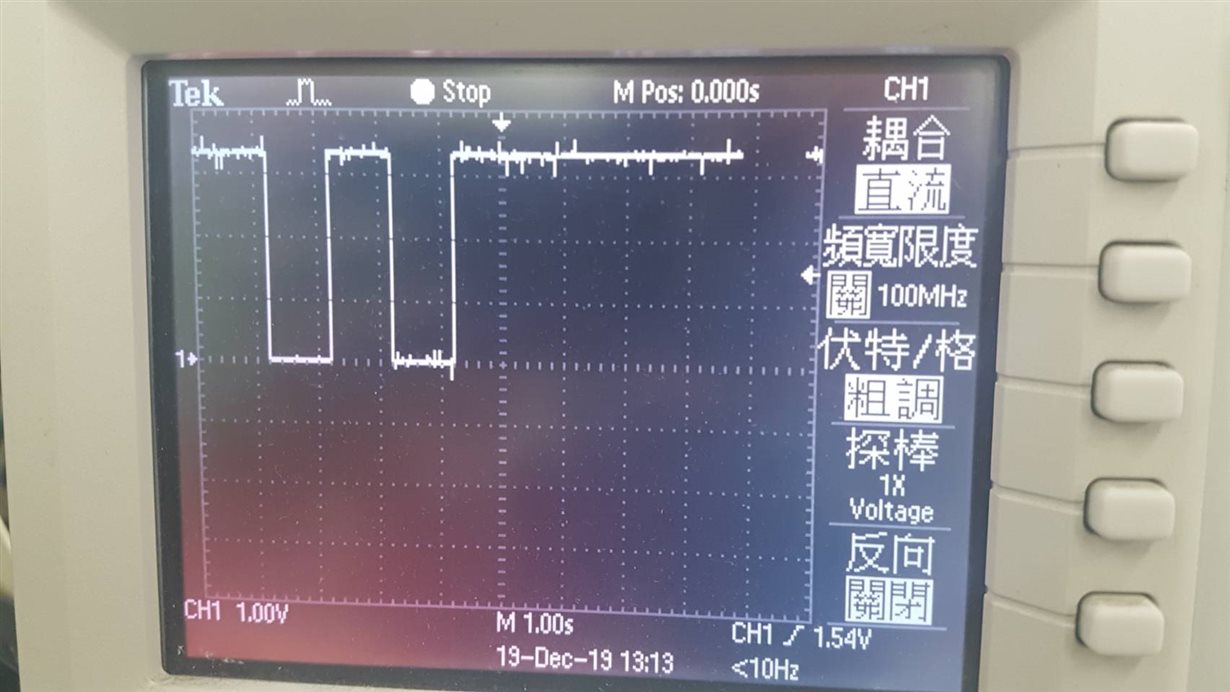

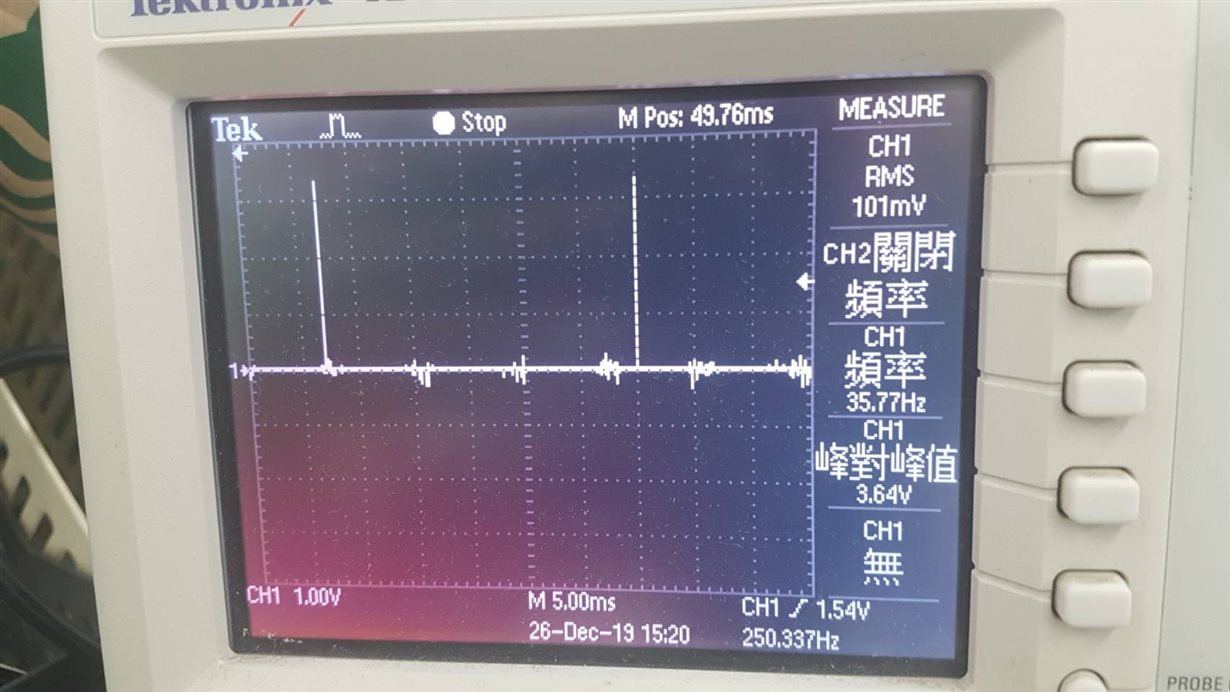

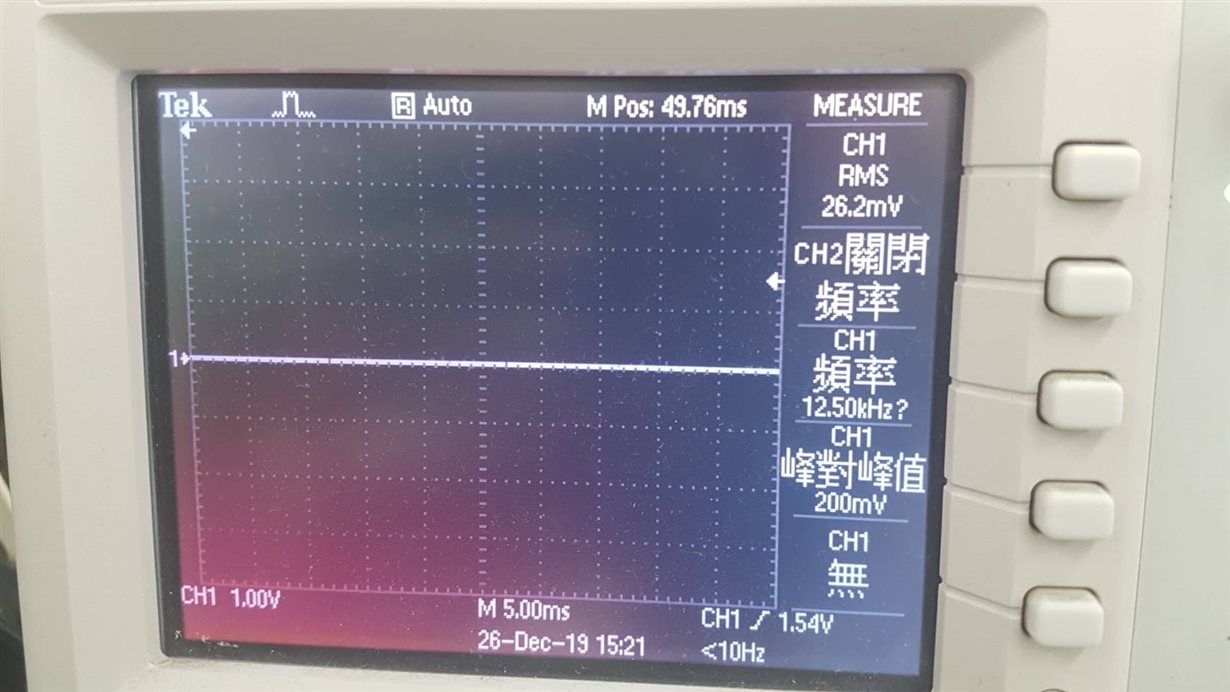

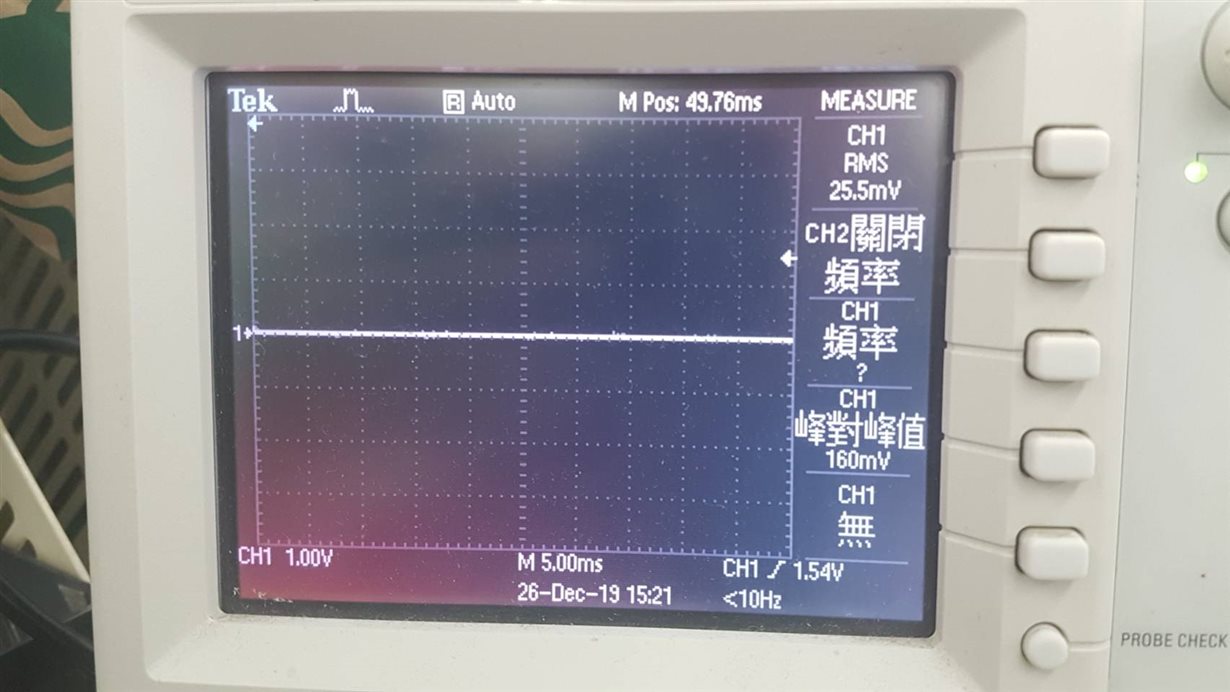

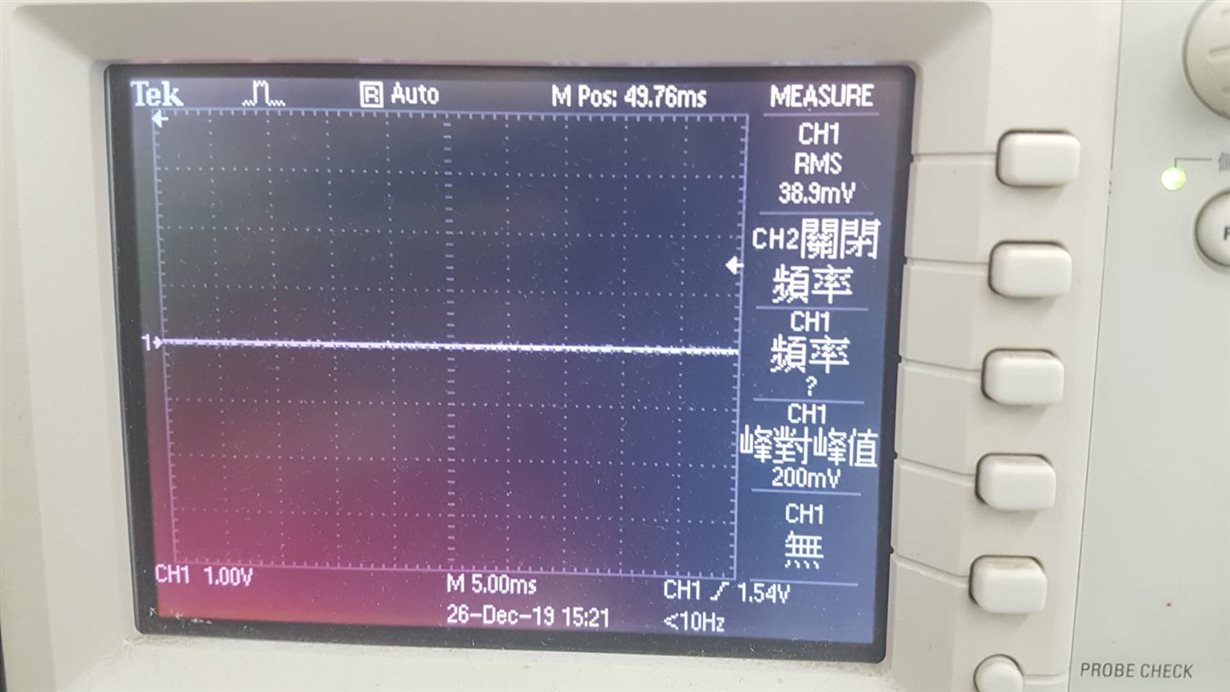

DRDY理論上應該跟數據表第58頁的步驟三一樣,應該是2.048MHz / 8192 = 250Hz,但是我的只有150Hz,並且我的SPI的CLK為LOW,DIN、DOUT則為High,而不是方波,請指教感謝!

#include "ti/devices/msp432p4xx/inc/msp.h"

#include <stdint.h>

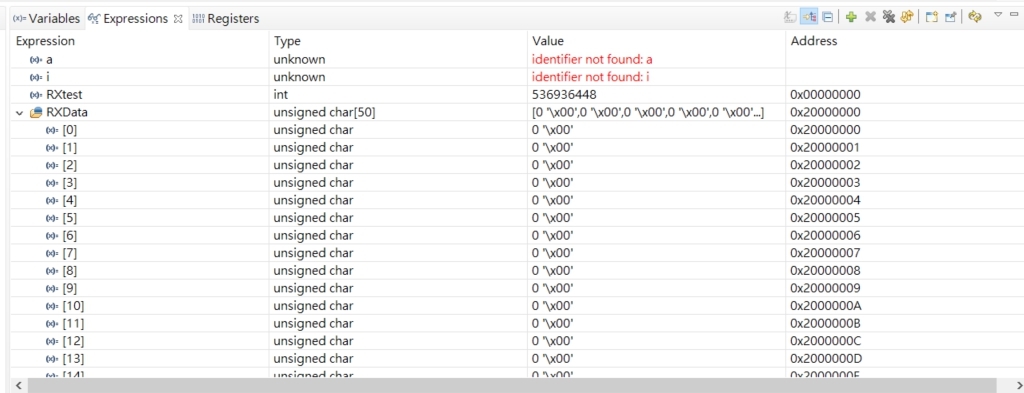

static uint8_t RXData[100];

static uint8_t TXData;

static char i;

#define HZ 3000000UL//3MHZ MCLK

int RXtest ;

int main(void)

{

////////////////////////////////////////////////////SPI////////////////////////////////////////////////////////////////////////

WDT_A->CTL = WDT_A_CTL_PW | // Stop watchdog timer

WDT_A_CTL_HOLD;

P1->SEL0 |= BIT5 | BIT6 | BIT7; // Set P1.5, P1.6, and P1.7 as

// SPI pins functionality

//P3->DIR |= BIT0; // P3.0 set as output CS

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_SWRST; // Put eUSCI state machine in reset

EUSCI_B0->CTLW0 = EUSCI_B_CTLW0_SWRST | // Remain eUSCI state machine in reset

EUSCI_B_CTLW0_MST | // Set as SPI master

EUSCI_B_CTLW0_SYNC | // Set as synchronous mode

EUSCI_B_CTLW0_CKPL_OFS | // Set clock polarity low

EUSCI_B_CTLW0_CKPH | //Phase high

EUSCI_B_CTLW0_MSB; // MSB first

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_SSEL__ACLK; // ACLK

EUSCI_B0->BRW = 0x01; // /2,fBitClock = fBRCLK/(UCBRx+1).

EUSCI_B0->CTLW0 &= ~EUSCI_B_CTLW0_SWRST;// Initialize USCI state machine

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

CS_Low();

__delay_cycles(HZ);

P5->DIR |= BIT1;

P5->OUT = BIT1; //PWDN High

__delay_cycles(HZ);

P2->DIR |= BIT7;

P2->OUT ^= BIT7; //RESET Low

__delay_cycles((4*HZ)/1000);

P2->DIR |= BIT7;

P2->OUT = BIT7; //RESET High

__delay_cycles(HZ);

P2->DIR |= BIT6;

P2->OUT |= BIT6; //Set Start High

__delay_cycles(HZ/1000);

P3->DIR |= BIT5;

P3->OUT = BIT5; //CLKSEL High

__delay_cycles(HZ/1000);

__delay_cycles(HZ/1000);

WREG(0x00 + 0x40,0x10); //channel1 Normal electrode input 0x60

WREG(0x01 + 0x40,0x96);//Config1 92=>4K 採樣率

WREG(0x02 + 0x40,0xD0);//Config2 0xC0

WREG(0x03 + 0x40,0xE0);//Config3

WREG(0x04 + 0x40,0x00); //LOFF

WREG(0x05 + 0x40,0x65); //channel1 Normal electrode input 0x60

WREG(0x06 + 0x40,0x65); //channel2

WREG(0x07 + 0x40,0x65); //channel3

WREG(0x08 + 0x40,0x65); //channel4

WREG(0x09 + 0x40,0x65); //channel5

WREG(0x0A + 0x40,0x65); //channel6

WREG(0x0B + 0x40,0x65); //channel7

WREG(0x0C + 0x40,0x00); //channel8

WREG(0x0D + 0x40,0x00); //BIASSENSP

WREG(0x0E + 0x40,0x00); //BIASSENSN

WREG(0x0F + 0x40,0x00); //LOFF_SENSP

WREG(0x10 + 0x40,0x00); //LOFF_SENSN

WREG(0x11 + 0x40,0x00); //LOFF_FLIP

WREG(0x12 + 0x40,0x00); //LOFF_STATP

WREG(0x13 + 0x40,0x00); //LOFF_STATN

WREG(0x14 + 0x40,0x00); //GPIO

WREG(0x15 + 0x40,0x00); //MISC1

WREG(0x16 + 0x40,0x00); //MISC2

//P2->DIR |= BIT6;

//P2->OUT = BIT6; //Set Start High

//__delay_cycles(HZ);

RDATAC();

RXData[i] = EUSCI_B0->RXBUF;

}

void spiTx (uint8_t byte)

{

while(EUSCI_B0->IFG & EUSCI_B_IFG_TXIFG)

{

EUSCI_B0->TXBUF = byte; // Transmit characters

}

}

void spiRx (void)

{

if (EUSCI_B0->IFG & EUSCI_B_IFG_RXIFG)

{

// USCI_B0 TX buffer ready?

RXtest = 1;

// Echo received data

}

RXData[0] = EUSCI_B0->RXBUF;

}

void CS_High (void)

{

P3->DIR |= BIT0; //Set P3.0腳位

P3->OUT = BIT0; //CS_High

}

void CS_Low (void)

{

P3->DIR |= BIT0;

P3->OUT ^= BIT0; //CS_Low

}

void RESET(void)

{

spiTx(0x06);

__delay_cycles((12*HZ)/1000000);

}

void SDATAC(void)

{

spiTx(0x11);

__delay_cycles((4*HZ)/10000);

}

void WREG(uint8_t _address, uint8_t value)

{

uint8_t opcode1 = _address + 0x40;

spiTx(opcode1);

spiTx(0x00);

spiTx(value);

}

uint8_t RREG(uint8_t _address)//在RDATAC模式下,RREG指令會被忽略(datasheet P35)

{

uint8_t opcode1 = _address + 0x20;

spiTx(opcode1);

spiTx(0x00);

}

void RDATAC(void)

{

spiTx(0x10);

__delay_cycles((3*HZ)/1000);

}

void START(void)

{

spiTx(0x08);

}

void Testsignal(void)

{

void SDATAC();

__delay_cycles(HZ);

WREG(0x02 + 0x40,0xD0);

WREG(0x05 + 0x40,0x05);

void RDATAC();

}