请问AFE5808中的DCLK和FCLK比例不对是为什么呢?是不是哪里没有配置正确呢?

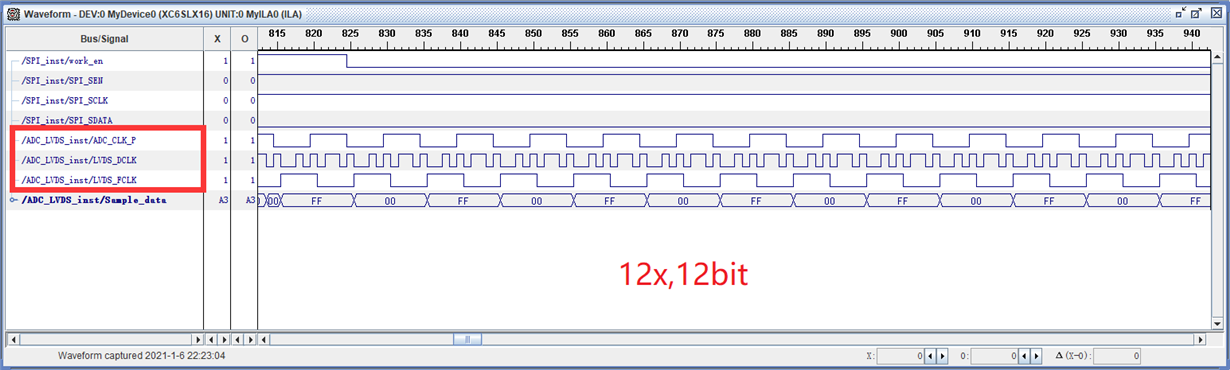

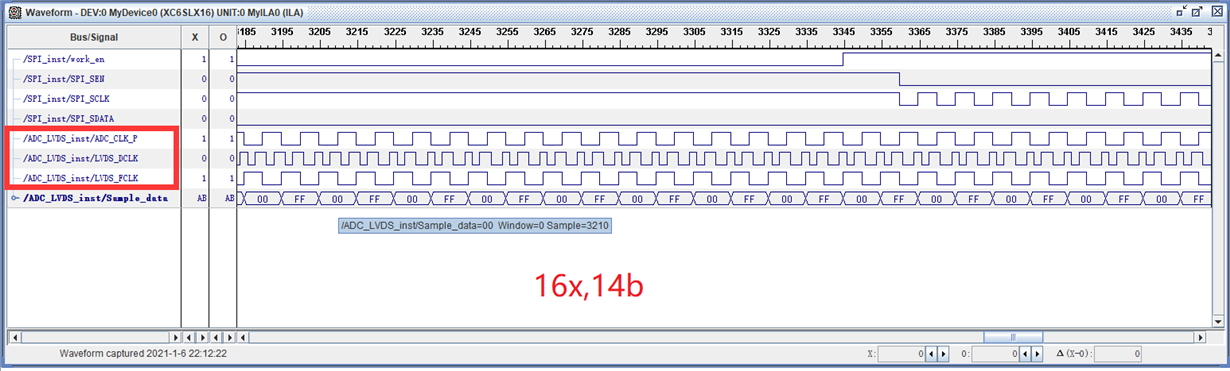

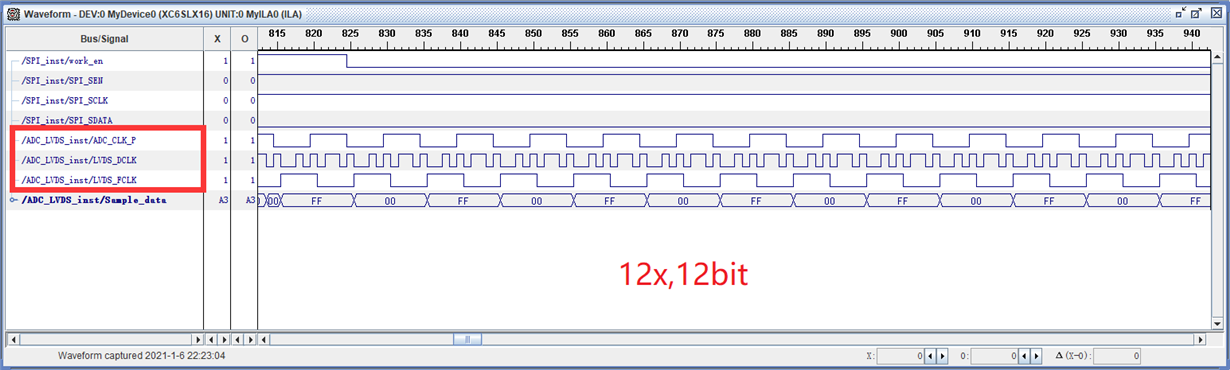

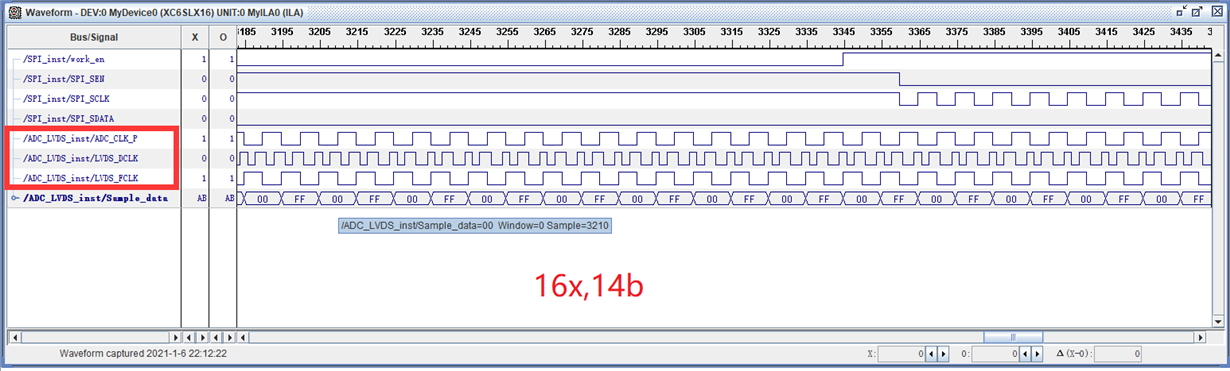

将寄存器配置为12x,12bit时DCLK和FCLK的关系如图1,将寄存器配置为16x,14bit时DCLK和FCLK的关系如图2。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请问AFE5808中的DCLK和FCLK比例不对是为什么呢?是不是哪里没有配置正确呢?

将寄存器配置为12x,12bit时DCLK和FCLK的关系如图1,将寄存器配置为16x,14bit时DCLK和FCLK的关系如图2。

您好,和您再确认下, 测试的这个DCLK和FCLK时序,是在AFE5808的输出端直接测试的吗?

这个不是输出端直接测的,这是连接到Spartan-6上面使用chipscope测出来的波形。我觉得很奇怪的一个点是12bit 12x的FCLK和DCLK比例比14bit 16x的时候还要高,正常同样的硬件下,不应该是12x的比例更低吗