Other Parts Discussed in Thread: DS90CF366

大家好~

我这边的硬件扑拓结构如下:

SOC <--DSI--> ds90ub941 serializer <--FPDLINK--> ds90ub948 deserializer <--oLDI--> ds90cf366 <--RGB--> display monitor (480x240)

(display的分辨率是480x240,通过SOC的DSI输出,DSI信号输入ds90ub941,ds90ub941通过1根同轴线连接ds90ub948,ds90ub948连接ds90cf366再连接屏幕)

ds90ub941配置的CLOCK Mode为0,即“FPD-Link III is generated from DSI clock. The DSI clock has to be continuous.”。

刚开始ds90ub941配置的dsi lane数是4(通过MODE_SEL0配置),display monitor不能显示。

ds90ub941的datasheet中很多地方都说支持的最小pixel clock为25Mhz,

比如在“8.3.2 High-Speed Forward Channel Data Transfer”这个章节中有如下描述:

The device supports pixel clocks in the range of 25 MHz to 105 MHz over one lane, or 50 MHz to 210 MHz over two lanes.

算了一下当前配置的pixel clock的频率,不足10MHz,更不足25HHz,

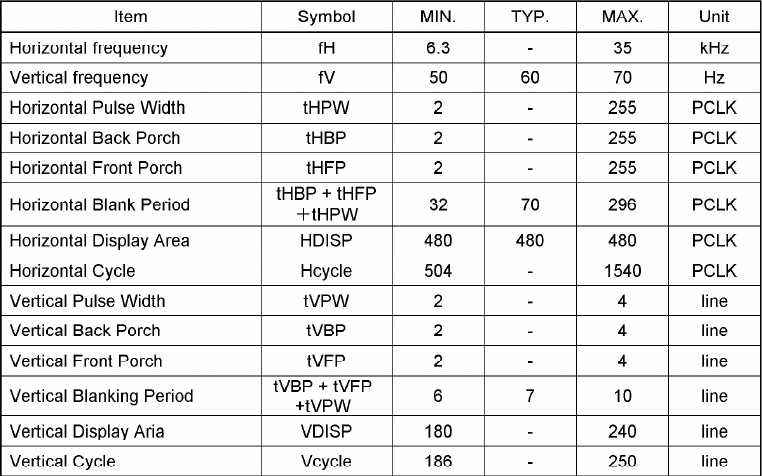

然后把HFP、FBP等参数设置得尽量大些,能够产生的pixel clock的频率为:

(480+64+64+64)*(240+3+3+3)*60=10039680=10.04MHz

10.04MHz仍不足25MHz。

后来把ds90ub941配置的dsi lane数改为1(通过寄存器0x4f修改),并把SOC输出DSI信号的dsi data lane数由4改为1,这时display monitor能显示了。

附件是能显示与不能显示时的ds90ub941的寄存器dump。https://e2echina.ti.com/cfs-file/__key/communityserver-discussions-components-files/58/i2c_5F00_dumps.7z

我有如下两个疑问:

1.

既然10.04MHz的pixel clock可以工作了,是不是可以理解为ds90ub941的datasheet中的如下这句话不准确呢?

The device supports pixel clocks in the range of 25 MHz to 105 MHz over one lane, or 50 MHz to 210 MHz over two lanes.

2.

dsi data lane数由4改为1后display monitor能显示了,是因为dsi data lane数由4改为1后DSI Clock lane的频率提高了吗?且DSI Clock lane和Reference clock有关进而fREFCLK的频率也提高到25MHz以上了?