1.视频输入板卡->FPGA->视频输出板(DP130)->4K显示器,画面显示正常;

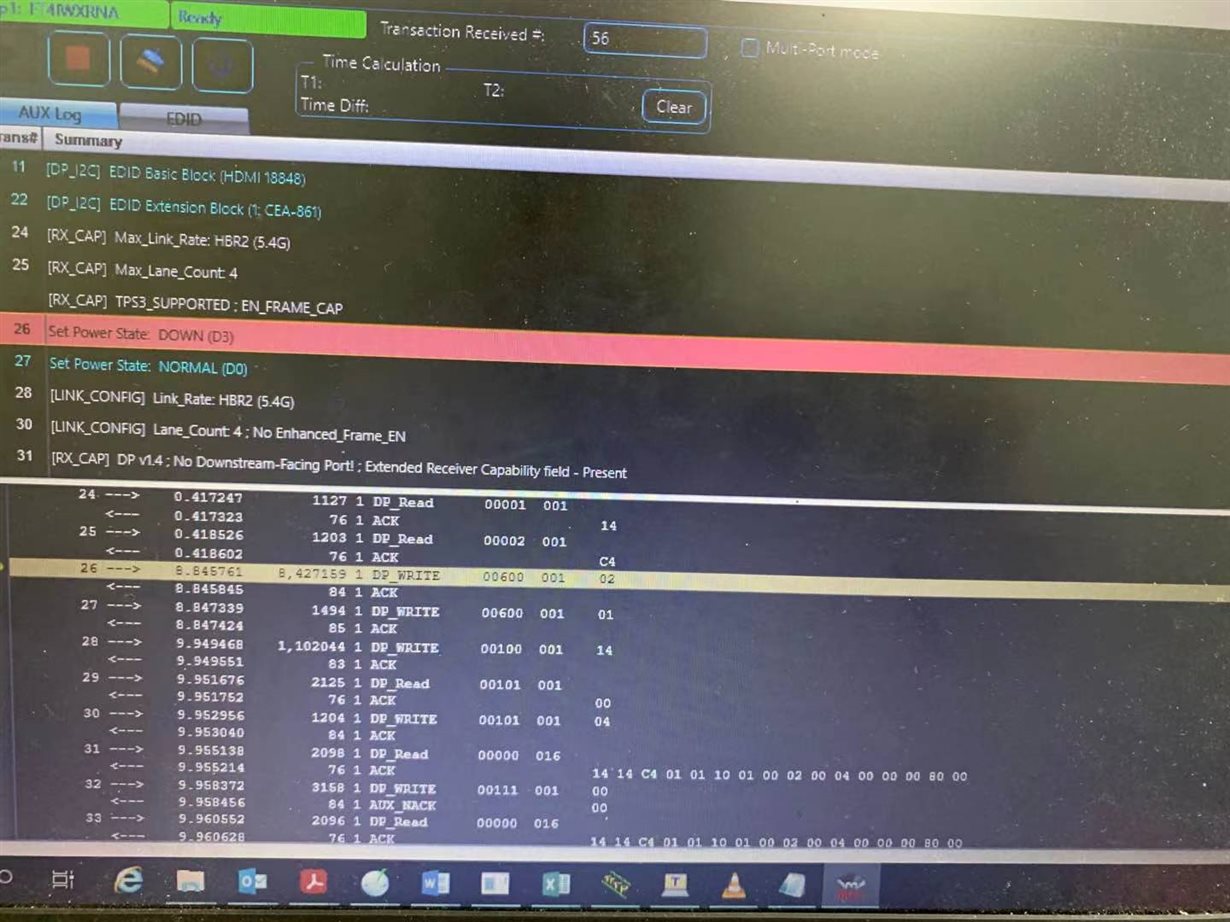

2.视频输入板卡->FPGA->视频输出板(DP130)->分析仪报错 link failed;

3.视频输入板卡->FPGA->视频输出板(DP130)->视频输入板(ITE6563+ITE68051), 无法识别;

4.FPGA测试程序,固定输出->视频输出板(DP130)->视频输入板(ITE6563+ITE68051), 画面显示正常;

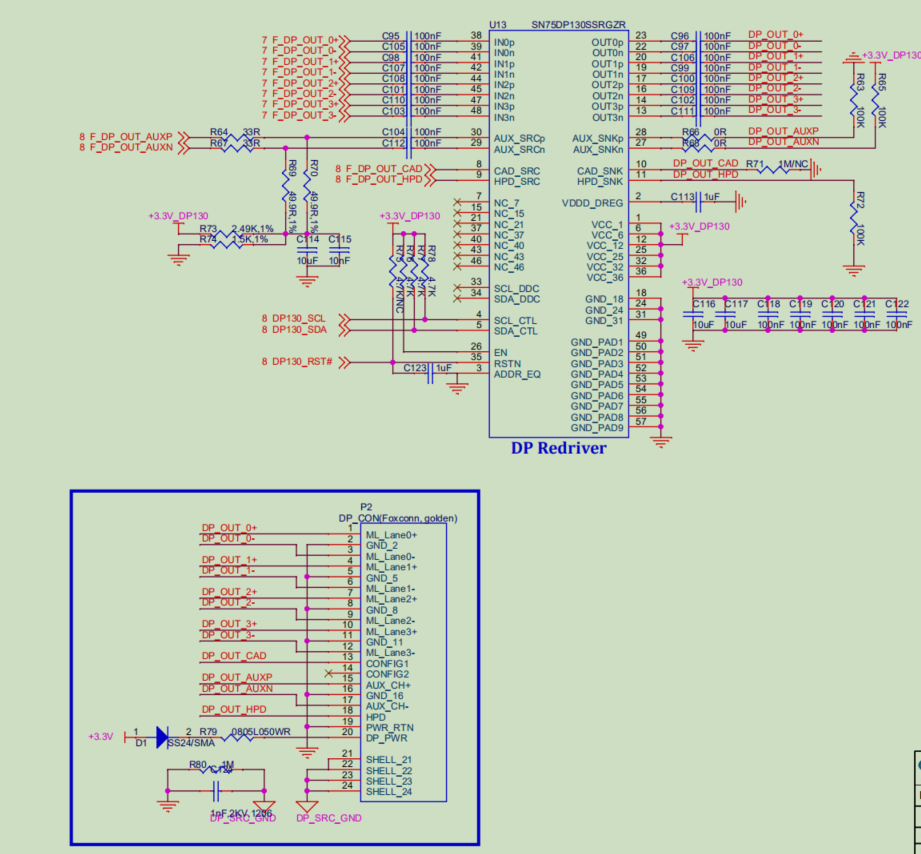

怀疑时AUX通道造成的影响,请问该怎么定位问题,下面时DP130应用原理图