按照手册上的初始化流程每一步反馈信号均正常,到最后输出ADC通道数据时发送NULL指令查询状态返回0x2214,查询手册发现存在F_ADCIN和F_RESYNC两种错误。

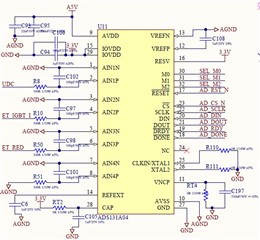

其中查询STAT_P寄存器状态返回0x2309,发现AXIN4和AXIN1超量程,本次使用内部参考电压4V,只是用了AXIN2输入5V电压,AXIN1预留了外部输入端口但未使用,AXIN4接地,请问F_ADCIN错误该如何解决?

另外想请教引起F_RESYNC的原因是什么,板子上只是用了一块ADS芯片,使用的是同步从机模式,采用FPGA做主机控制,我将DRDY_N与CS_N相连输出给ADS芯片,还麻烦大佬帮忙解答。