Other Parts Discussed in Thread: ADS9224R

用FPGA控制ADS9234R实现数据采集,当使用ADS9234R的缺省配置(复位之后的状态)、利用1路数据(SDO0A/SDO0B)数据接口读取ADC数据,能够正确读取2个通道的数据,但由于每通道只有1路数据输出,需要16个SPI读取时钟,受此影响ADC的采样速率受到限制,大约只有1.47Msps;

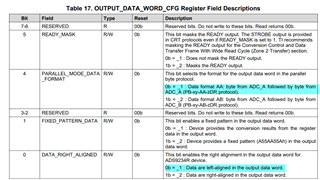

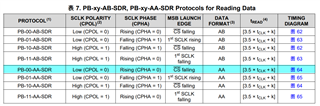

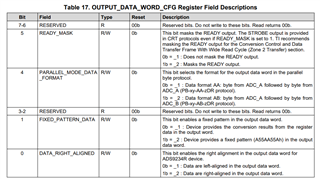

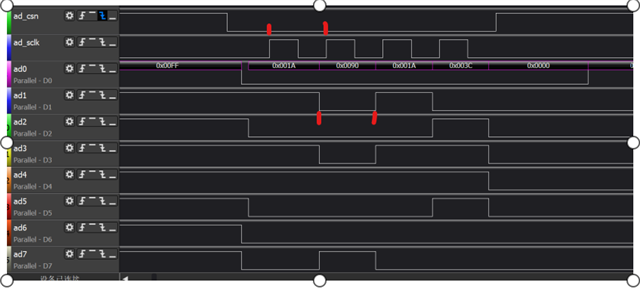

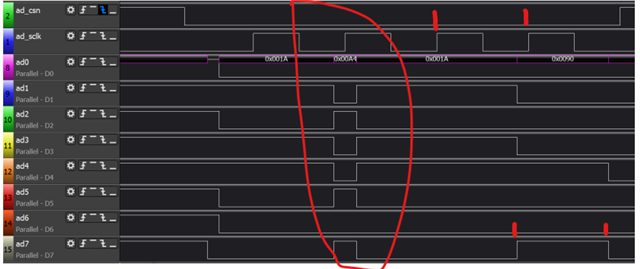

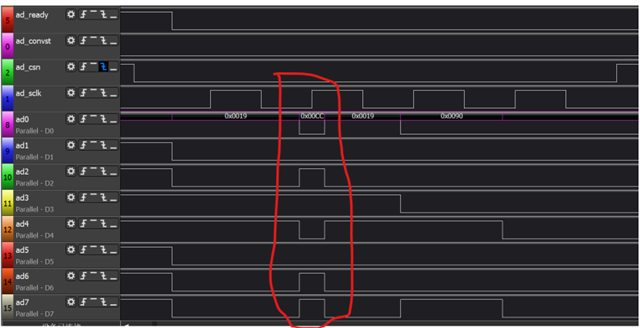

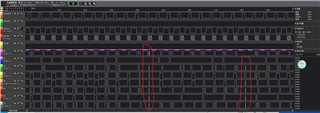

为了提高采样速率,需要更改其工作方式,比如设置成并行输出方式,按手册7.7.1.3的说明,可以用命令0x1240(op3-0=0001,a3-0=0010,sdo_protocol2-0=100,cpol=0,cpha=0),写入时序如下(FPGA内部在输出到ADS9234R引脚的同时引到其它FPGA引脚,用逻辑分析仪同步采集到的波形-----可惜波形还没找到上传的办法);如果复位之后,不发送0x1240的命令,ADS9234R只有SDO0A和SDO0B两路输出,而发送命令之后,sdo7-0均有信号输出(说明命令起作用了)。

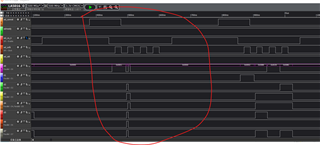

问题:1)当设置到并行模式后,读取ADC数据,结果只有ch0的数据是正常的,ch1的数据不正常,会有许多干扰(见下图);类似的控制,如果使用命令0x1302或0x1303(即SPI-2和SPI-4的方式)读取ADC数据,现象是一样的:ch0正确,ch1数据不对。(SCLK时钟速率是25MHz,一些图片没找到上传的办法)

因此,需要请教一下如何正确配置ADS9234R内部的工作方式,如何正确读取并行方式下的数据,其时序逻辑有何要求。当我们只需要修改成并行数据接口方式,只要发送前述0x1240的命令,还是还需要同时发送其它命令(若需要则其命令码是什么)?发送命令和开始采集之间需要有什么时间间隔?

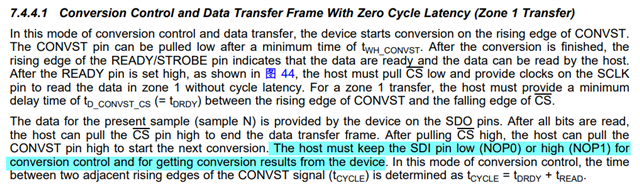

2)有关ZONE2方式,是否只要在convst上升沿之后的15-180ns内启动有效的cs(变低电平)及其读取时序,就可以自动进入zone2读取模式?手册7.7.1.1有关状态寄存器0的bit2只是方式的状态指示(当bit2=1),当被清零时退出Zone2方式?