Part Number: ADS8671

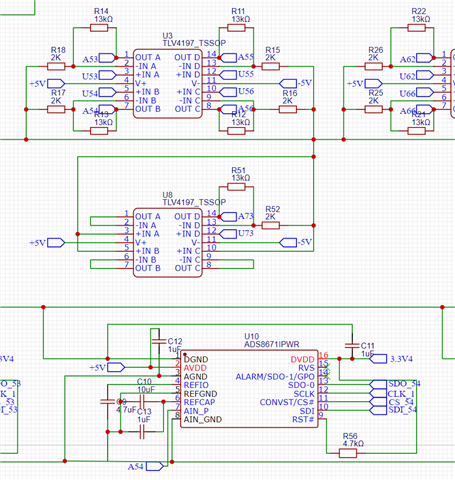

我们在使用ADS8671采集数据时,采集的是放大器放大后的信号,fpga在对ADS8671没有任何写入操作,也就是使用默认配置,采集的幅值为+-12.288V,使用示波器观察运放放大后的信号,再与fpga采集的信号对比,发现fpga采集的信号的幅值为放大后信号缩小的4.5-5.5倍。电路如图。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,您的意思是放大器输出+-12.288V是没有问题的是吧?但是发现fpga采集的信号的幅值为放大后信号缩小的4.5-5.5倍,这个是测量的哪里? ADC的输入端吗?

您好,抱歉回复晚了,不知您的问题解决了没。

放大器的输出是正常放大后的信号,也就是ADC的输入是放大后的信号,两个引脚都测量过

ADC的输入即为运放的输出,, 根据您的配置,输入电压范围应该是在+-12.288V之内,此时两个引脚的测试电压都是正常的是吗?

那么运放的输出电压是多少?

正常的话给ADC输入1.5mv是可以检测到的,但是实际测试时,只有输入5mv及以上的信号才能被检测,ADC读取的值+1

现在遇到的问题是,ADC 输入只有在5mV以上才能检测到是吗?您是怎么测试的。

因为如果配置了输入为+-12.288V范围的话,1.5mV也在这个范围内,是能采集到的

您好,+-12.288V的话,-12.288V对应的code是0000h,12.288V的话对应的是3FFFh。

CS由高到低的过程中,当CS为low的时候,先读取的最高位,为3FFFh,是没问题的。

您提到的电压缩小了4.5~5.5倍,是根据output code*LSB 计算的Vin,然后确定的是吗?

您好,您的计算有误,Vin=output code*LSB.而LSB=m*Vref/Gain

您可以参考这两篇FAQ, 关于怎样将ADC的输出code转化为电压的。有part 1和part 2,介绍的非常详细,希望对您有所帮助:

在尝试更新算法后,(也就是当最高位为0时是正电压,为1时是负电压,且是按照补码形式传输。转化为有符号的十进制以后乘上0.0015V就是实际的输入电压。)这样得出的结果的幅值依旧出现了缩小了4.5~5.5倍

您好,当ADC输入为+-12.288V 输入的时候,得到的output code是多少?

您好,还有几个问题要和您确认下:

REFIO和REFCAP的电压都是多少? +-12.288V 的输入是在靠近ADC输入端测量的吗?要确保它是采样电压的最大最小值,而不是在其他位置测量的。还有麻烦提供下SCLK,CS,SDI和SDO的SPI的时序,建议稍微放大一些的时序图看下。

逻辑分析仪的时序太紧密了,可以用示波器测量下时序附上吗?

另外,SPI的SCLK是100Mhz还是50Mhz? 如果是100Mhz,超过的了最大66.7MHz的要求。

麻烦不上示波器测量时序再帮您分析下。

抱歉回复晚了。

关于您的问题

1.建议降低了 SCLK 频率并再次验证。因为从波形来看, SCLK 显示了明显的干扰信号、这可能会导致读数错误、您必须弄清读数的来源并将其删除。

您的基准电压是正确的、即使它不是很精确,因为您正在使用示波器进行检查。

另外,在没有 AIN_P 输入的情况下查看 SDO 上的代码是正常的、因为当 AIN_P 悬空时、ADC 将输出内部偏置电压。 信号连接到 AIN_P 输入后、ADC 将输出模拟输入的转换代码。

使用可用的 AIN_P 输入时、很难检查 SDO 输出是否正确、因为 SDO 和 SCLK 的时序显示在不同的图中。 您能否在相同的时间内捕获 SDO、SCLK、/CS 和 SDI? 低于12V 的直流输入将非常适合用于测试目的、因为12.3V 超出了最大输入范围。

您好,您的计算有误,Vin=output code*LSB.而LSB=m*Vref/Gain

您可以参考这两篇FAQ, 关于怎样将ADC的输出code转化为电压的。有part 1和part 2,介绍的非常详细,希望对您有所帮助:

您在这里给出的回复,这里面的计算是补码二进制,也就是说当14位全为1的时候,转换后的电压应该是负的,但是手册里面是直接二进制,当14位全为1 的时候,转换后的电压应该是正的,也就是12.288-0.0015V您对比一下