输出两个点的时间间隔,最短多少?

我看时钟是50MHz

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

输出两个点的时间间隔也就是更新时间,它是由数字接口的更新时间(update time)或 稳定时间( settling time)决定,哪个时间长由哪个决定。

计算数字接口的更新时间:

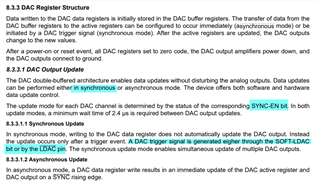

假设 SPI SCLK 的时钟频率为50MHz,根据Figure 7-1时序图,更新一个24bits的样本,需要的最小时间为tCSHIGH+tCSS+23*tsclk+tCSH=505ns;

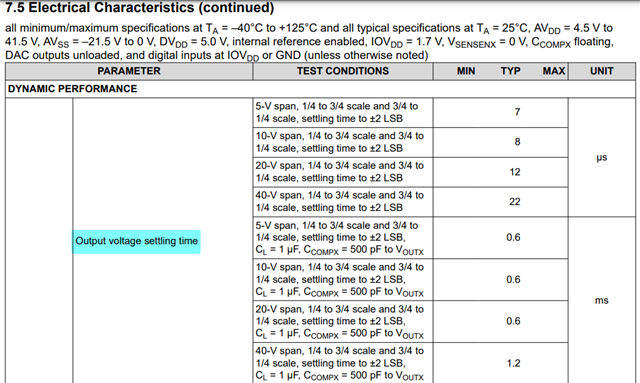

DAC81402的 settling time如下截图,给出的是 DAC 从1/4*全刻度范围步进至3/4*全刻度 的稳定时间, 这不是最快的稳定时间。如果 DAC 仅步进1 LSB,则更新时间会更短,因为 DAC 的小信号稳定速度要快得多。它同时与负载电容CL有关,CL越大settling time越长;可以看出 其settling time是us级的,

因此,DAC81402的更新时间不受数字接口的限制,而是取决于稳定时间:

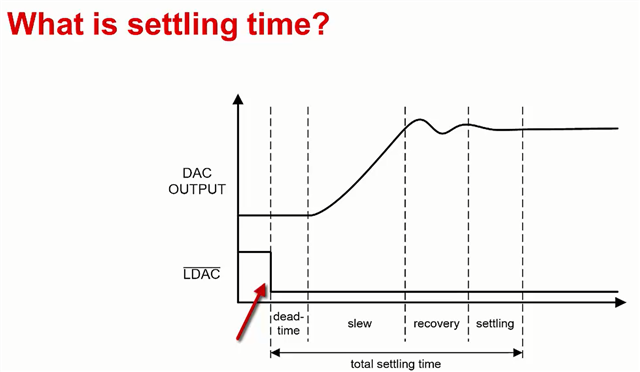

settling time不是说怎样输出的问题,它是输出后多少时间能达到稳定多少范围的问题,一般是±2LSB,它输出后总的settling time包括dead time 、Slew 、recovery 、settling 时间;

关于settling time和update time,更多信息请查看下面视频,视频中有详细讲解:

Daisy-Chain 是需要使用多个DAC设备(或ADC设备)时,数据串行接口连接的一种拓扑结构,在数据表8.5.2 Daisy-Chain Operation有说明。

您的意思是说工作在synchronous模式下吗?可以的,需要DACA和DACB的 SYNC_EN 位置1使能synchronous模式,可以SOFT-LDAC bit 或 LDAC pin触发输出