您好,我通过XLINX的V7690T控制ADS54J60,在819.2MHz的采样时钟下稳定运行,能够采样到正确数据,选用8224模式。

但是当我想尝试在500MHz采样率下工作,通过修改FPGA的JESD204B IP核相关参数,降低信号源输出频率到600MHz以下时,同步信号(RX_SYNC)拉低,经测试585MHz为临界点。而且当204B同步信号拉低后,调高信号源采样率为600MHz,同步信号依然不能拉高,重新加载FPGA程序无效,只能给板卡重新上电才能解决,这是为什么呢?

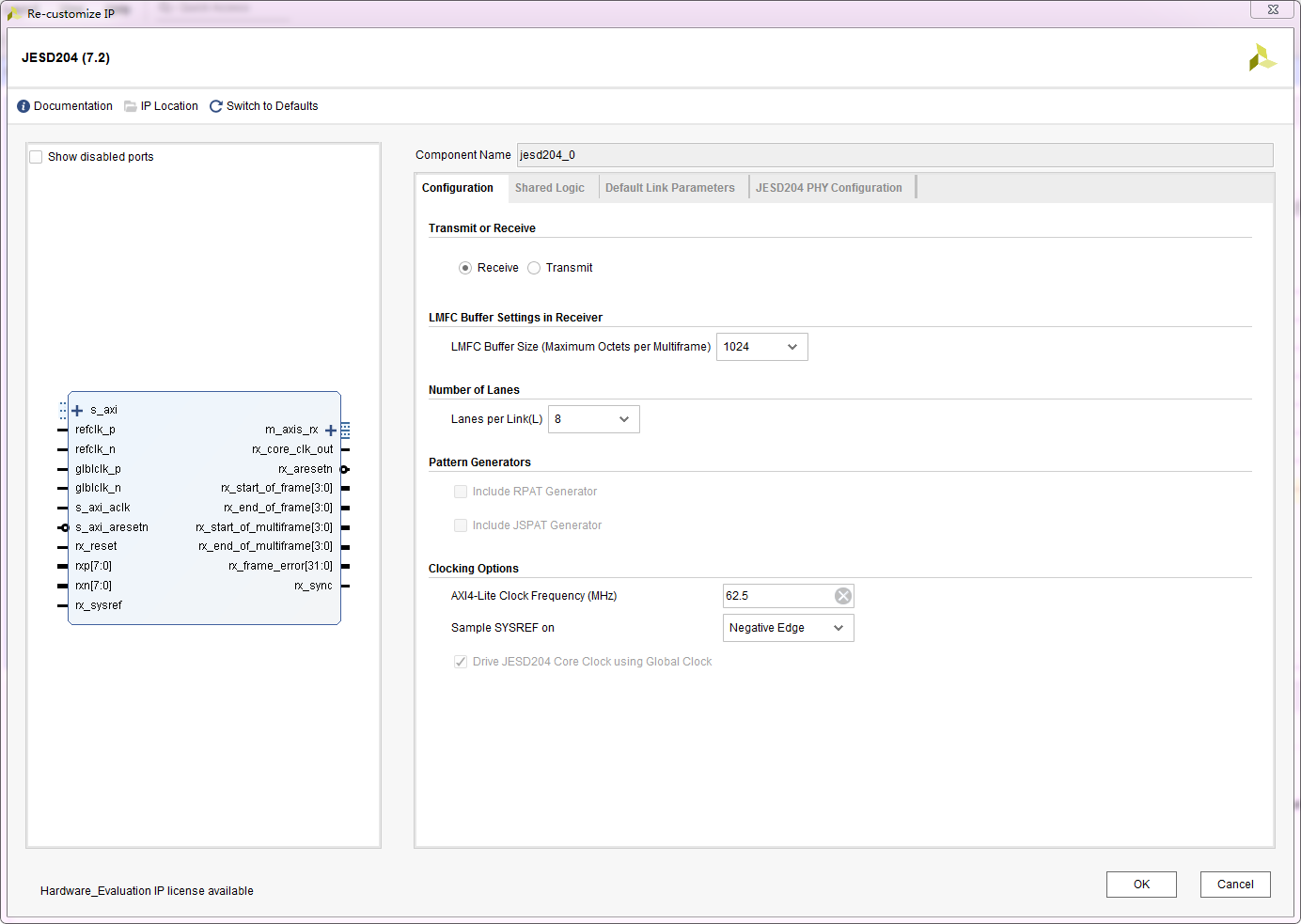

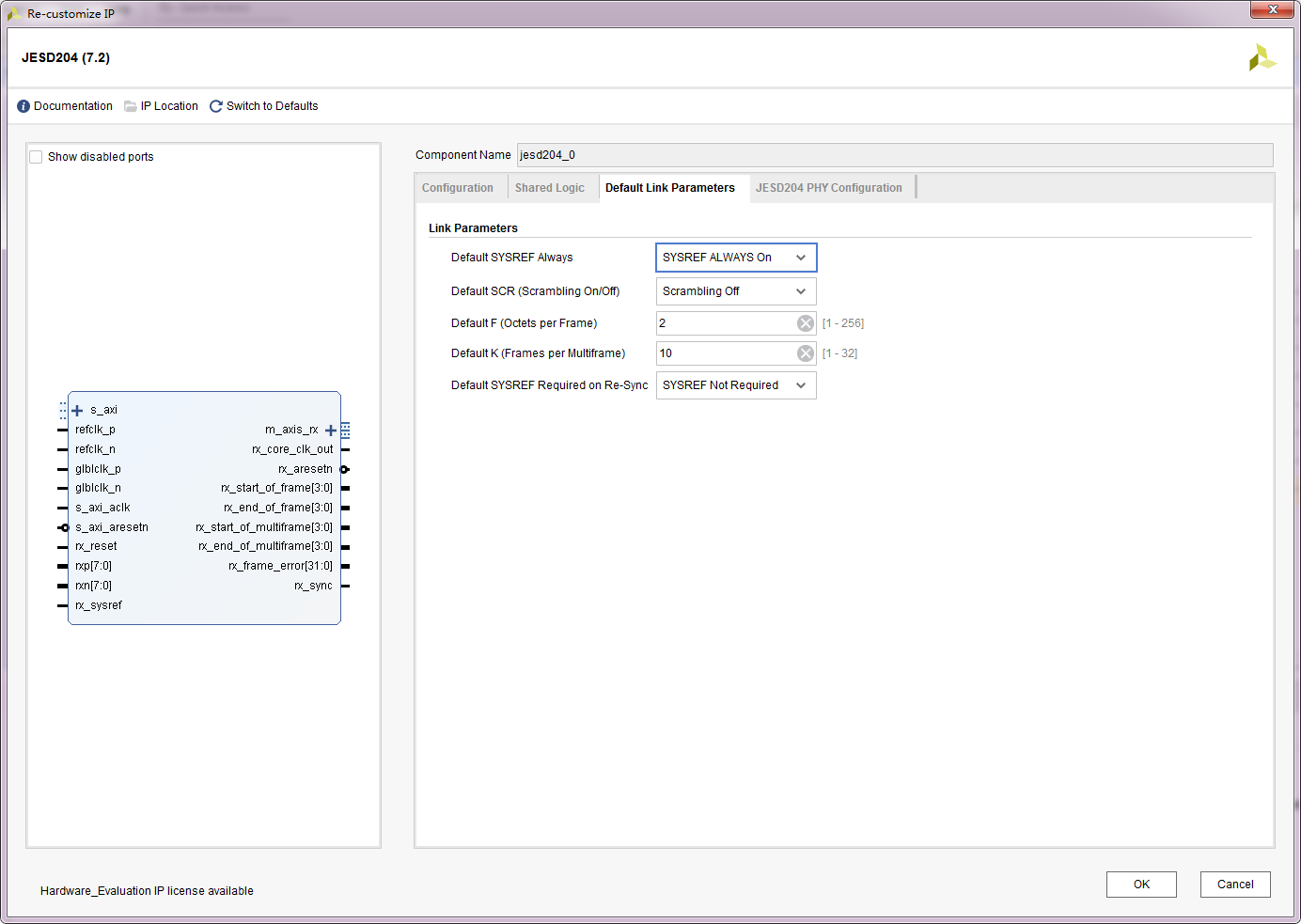

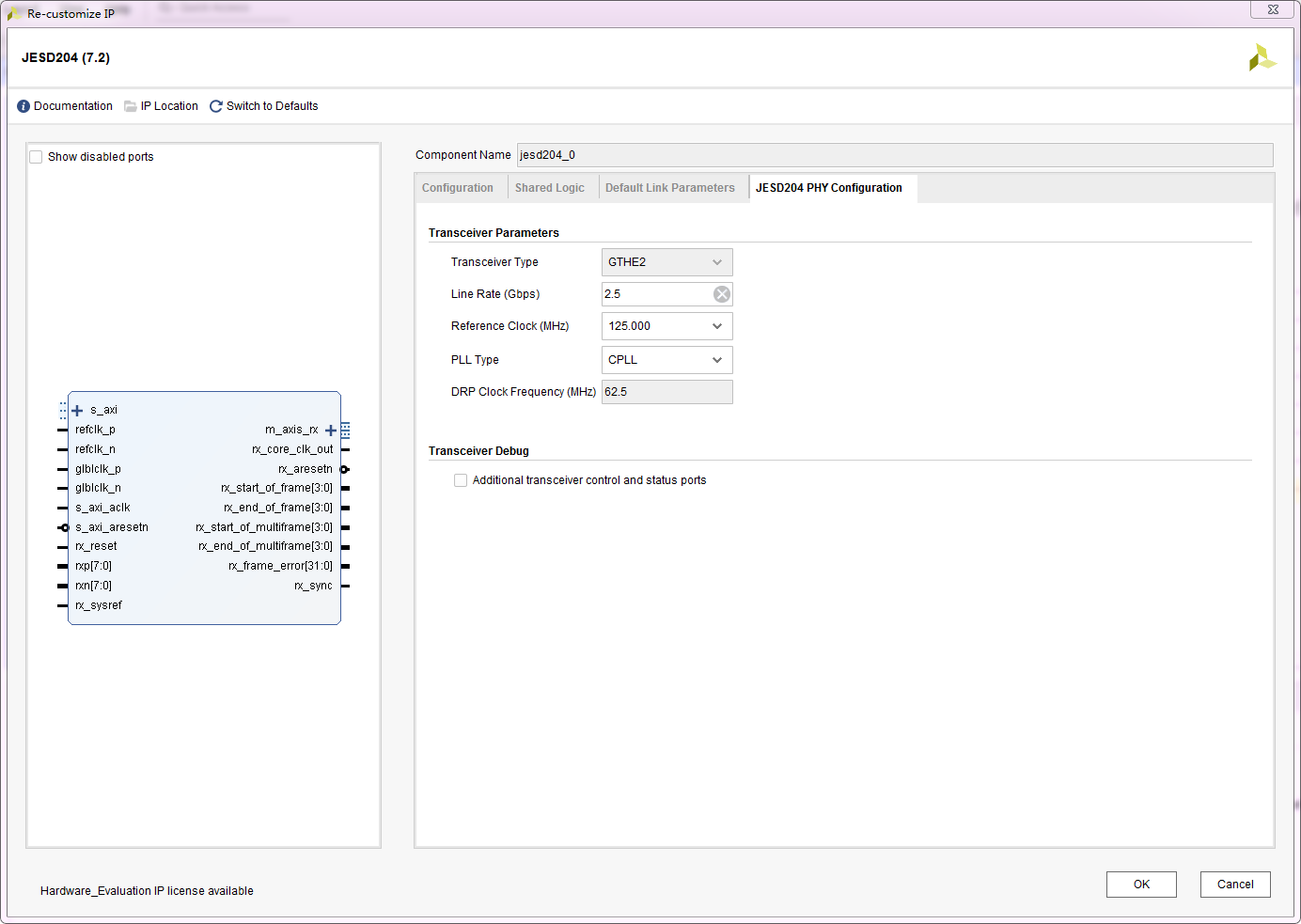

下图是我FPGA的JESD204B配置图,目标是实现500MHz采样