Other Parts Discussed in Thread: TMS320C6678,

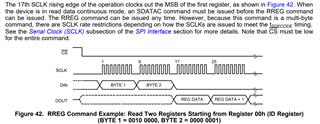

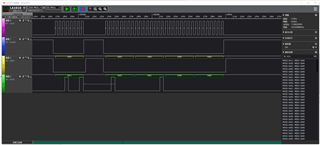

根据datasheet的说明,我先发送SDATAC指令,随后延时2μs(频率为2MHz),然后发送0x20 0x01(ID寄存器地址为00h),得到如下的波形。

似乎我发送数据之后,ADS131E08并没有任何反应,想请问一下可能是哪里出现了问题?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

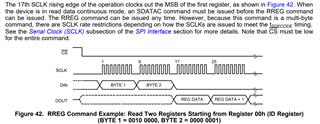

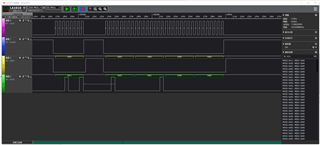

根据datasheet的说明,我先发送SDATAC指令,随后延时2μs(频率为2MHz),然后发送0x20 0x01(ID寄存器地址为00h),得到如下的波形。

似乎我发送数据之后,ADS131E08并没有任何反应,想请问一下可能是哪里出现了问题?

reset后还会出现脉冲的前提应该是START置1吧,如果START为0,还是没有脉冲。

是的,reset后就是拉低reset后又拉高,如果reset=0,那么设备一直处于reset状态,是不会发出DRDY脉冲的;

但是看CS波形,每格是20mV,那么CS在高电平时是不满足高电平要求的;

MISO是每格1V,看幅值也不满足高电平要求,ADS131E08输出高电平至少0.9*DVDD,即1.62V;

感觉应该是接线问题或者示波器探头设置问题,您交换下探头,看是否还是同样的现象?