Part Number: LM98725

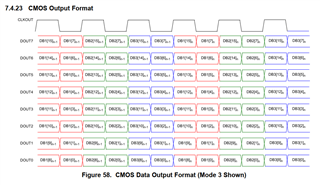

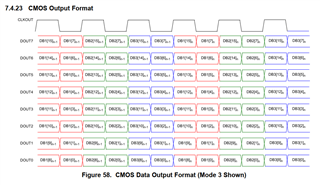

LM98725采用CMOS输出格式时为8bit*2的形式,我这边对接的芯片是8位DVP接口,但是软件上无法实现LM98725时序要求的上下降沿采样高八位,和低八位。仅能实现单种跳变沿的采样。即上升沿采样,或者下降沿采样。

请问是否有什么办法能解决这个问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LM98725

LM98725采用CMOS输出格式时为8bit*2的形式,我这边对接的芯片是8位DVP接口,但是软件上无法实现LM98725时序要求的上下降沿采样高八位,和低八位。仅能实现单种跳变沿的采样。即上升沿采样,或者下降沿采样。

请问是否有什么办法能解决这个问题。

感谢您的耐心!

美国工程师的回复大意是说,因为没有CLKOUT和INCLK之间关系的文档说明,不能确定其相位信号(内部电路中可能存在延迟)。 想让您提供使用该芯片的其他详细信息,比如连接原理图,因为这有助于更好地了解您的应用。

美国工程师的源回复如下:

I reached out internally to about your inquiry. It seems that CLKOUT is the same frequency as INCLK, but unsure about their phase signals (there could be delays within the internal circuitry).

Regarding your work around, its a bit difficult to say as the part does not have a lot of documentation about the device and the relationship between CLKOUT and INCLK (in regards to the phase signals). Can you provide additional details on how the customer is utilizing the device with the workaround?

Best regards,

关于二倍频电路的方法,我也咨询了美国工程师的意见,他说这种方法可能会起作用,但客户需要用自己的系统验证该方法(the Doubled CLKOUT method may work, but the customer needs to verify this method with their own system)。

关于推荐二倍频IC,TI没有相对简单的合适芯片,功能都比较复杂,不过下面链接电路是一个较简单的二倍频电路,它是使用比较器和异或逻辑门来生成的倍频信号:

https://www.maximintegrated.com/en/design/technical-documents/app-notes/3/3327.html