Other Parts Discussed in Thread: TPD4E1B06

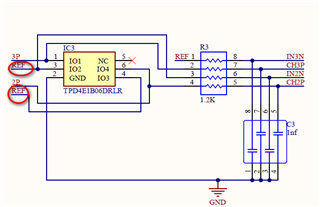

我采用伪差分输入,只使用输入通道的P引脚。请问我的原理图设计有什么问题吗?在上方的防静电模块设计正确吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

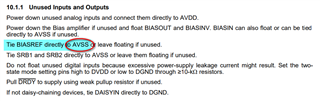

1、不使用的模拟输入管脚直接接AVDD,没有错;

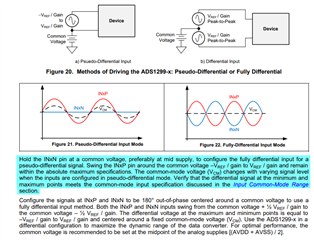

2、关于伪差分输入,一般建议将INxN引脚接在中间电源电压,在±2.5V供电时,供电电源的中间电压是0V,这样可以为伪差分信号配置全差动输入。另外注意输入差分电压满足–VREF / gain至 VREF / gain范围,且输入共模电压满足datasheet 9.3.1.3.1 Input Common-Mode Range这章节中的要求。

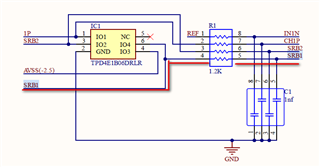

3、关于SRB1网络,在电阻1.2K两端同时接SRB1,那么这个1.2K电阻相当于没有接入电路中;

SRB2网络,同样的问题;

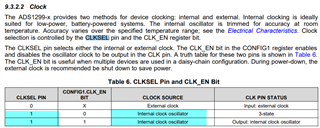

4、CLKSEL接高电平的话,是使用内部时钟源,那么CLKpin就不需要外接外部时钟源:

5、BIASREF不使用的话,是接AVSS,而不是AGND

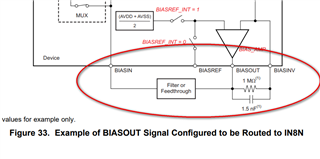

6、BIASOUT、BIASIN、BIASINV这三个管脚的连接,您应该是参考的datasheet Figure33,请确认这3个管脚的连接:

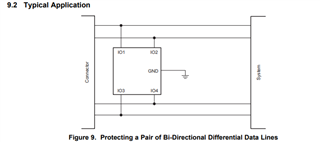

7、关于TPD4E1B06 的连接请参考其datasheet典型应用连接方式,即将信号线连接至其一个IO就可以了。

关于您这部分的连接,有些信号线,比如REF有多次连接到多个TPD4E1B06 IO的情况,这是没必要的,连接一次就可以了;

请注意,TPD4E1B06 应放置在connector附近;

其他电源电路等部分,请咨询电源工程师等相关工程师