Part Number: ADS131E06

Other Parts Discussed in Thread: ADS8556

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS131E06

Other Parts Discussed in Thread: ADS8556

您好,

装置在上电过程中容易出现ADC芯片寄存器配置失败,状态字错误等问题;

检查下是否满足 datasheet 中11.1 Power-Up Timing部分的上电顺序,然后再进行寄存器配置。

(2)在做群脉冲干扰试验时(试验等级:±2KV、5KHz;通过EFT耦合夹耦合到装置遥测板输入信号线上),ADC芯片必然会出现复位、寄存器配置值丢失、状态字错误等问题;

如您所说,ADS131E06 ESD防护等级为±1000V,试验等级±2KV,这超出了其防护等级,应该是这里的原因。

如果要过群脉冲干扰试验,我因为输入端需外加ESD IC。

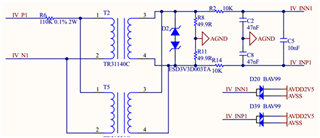

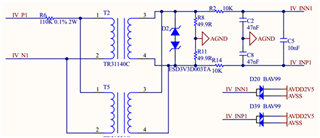

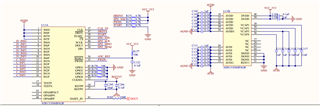

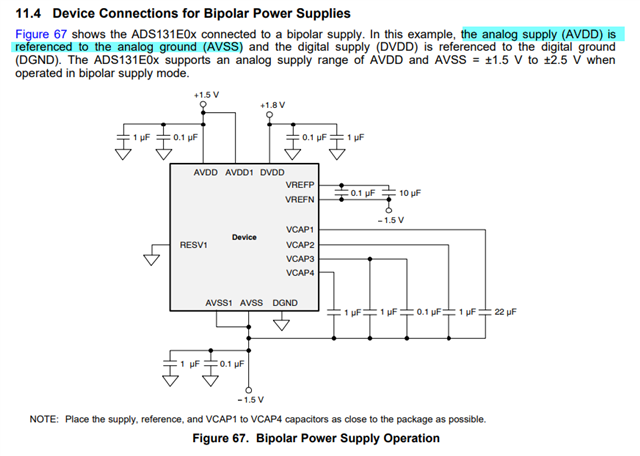

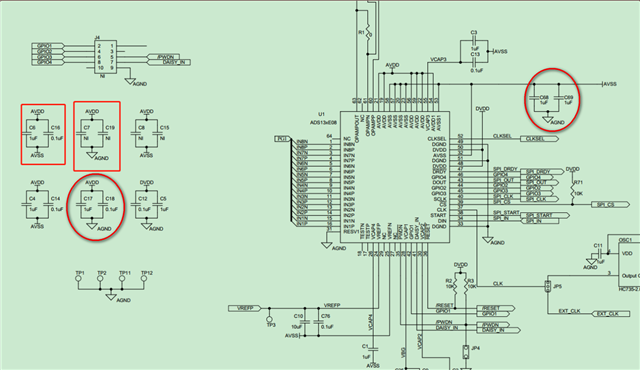

(4)ADS131E06芯片为±2.5V供电时,芯片AVDD和AVSS管脚的旁路退耦电容是分别对AGND而言?还是AVDD相对于AVSS放置电容,因为DEMO参考板上的处理方式两者都有,

建议按照datasheet说明连接,如下截图所示,因为DEMO板和Figure 67没有分开模拟地和数字地,所以都加了电容,如果分开的话,AVDD就是对AVSS加电容。

(2)会不会因为ADC芯片菊花链芯片数量太多,导致系统整体抗干扰性能不好?

菊花链主要是转换数据的数字输出方面,与采样值正确不正确有关,应该与复位、寄存器配置值丢失、状态字错误关系不大。

FAE:

您好!感谢回复!

针对问题中提到的群脉冲抗干扰试验,目前我们在互感器输出端(即ADC芯片的模拟信号输入端)增加了ESD器件,测试结果为:

(1)对于电流互感器通道(5A/2mA),在增加ESD器件后,能够通过群脉冲抗干扰试验;

(2)对于电压互感器通道(电流型电压互感器:2mA/2mA),在增加ESD器件后,依然不能通过群脉冲抗干扰试验;

我的理解是:

(1)对于电流互感器通道,由于互感器的输入输出匝数比较大,耦合到输出端的干扰信号幅度较弱。

(2)对于电压互感器通道,由于互感器的输入输出匝数比为1:1,耦合到输出端的干扰信号幅度较强,所以依然不能通过群脉冲抗干扰试验;

请问,对于电压互感器通道,还有什么防护措施吗?谢谢!

因国庆节假期前休假了,很抱歉回复这么晚!

很高兴电流互感器通道在增加ESD器件后能够通过干扰试验。

对于电压互感器通道,我想应该是选择的ESD器件不合适造成的,下面链接是TI的ESD静电保护系列视频,希望您观看后以确认所使用ESD器件是否合适

https://edu.21ic.com/lesson/1899

FAE:

您好!

针对群脉冲抗干扰问题,我们最近做了很多改进措施和验证,目前在群脉冲抗干扰效果和整改措施可行度上,总结出如下两条可行的整改措施:

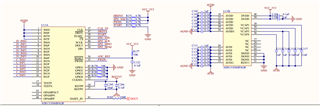

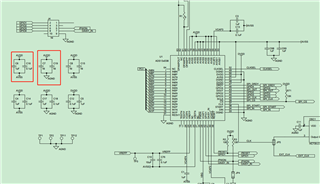

(1)措施一:ADC芯片模拟输入前端、供电电源、PWDN、复位等信号引脚上均添加共模ESD保护器件;

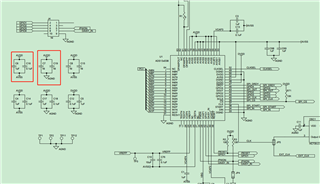

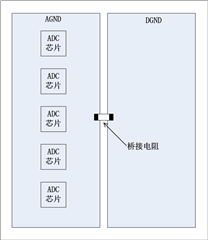

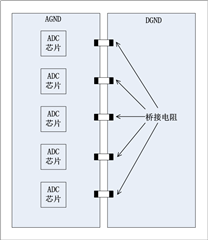

(2)措施二:将数字地DGND和模拟地AGND从单点桥接改为多点桥接,如下图所示;

测试现象及结果:

(1)如果只针对措施一进行整改,ADC芯片的群脉冲抗干扰效果有所改善,但是不能完全避免;

(2)在措施一的基础上,在按照措施二进行整改,ADC芯片的群脉冲抗干扰效果会得到大幅改善,失败次数减少很多;

我们的疑问:

(1)此处AGND与DGND的单点桥接和多点桥接,导致ADC芯片群脉冲抗扰度效果不一致的原因主要是什么?是因为ESD保护管泄放的能量从AGND到DGND的阻抗不连续,导致泄放能量形成辐射干扰?

(2)对于该ADC芯片本身而言,由于没有分模拟地AGND引脚和数字地DGND引脚,那么对于此类ADC芯片,是否需做模拟地AGND和数字地DGND的分割处理?如果不做模拟地AGND和数字地DGND的分割处理,ADC的采样精度会不会影响很大?

望尽快回复,谢谢!

1、您这里是采用0Ω电阻连接的AGND与DGND 吗?

是因为ESD保护管泄放的能量从AGND到DGND的阻抗不连续,

我想可能是这里的原因,0Ω电阻在通过高频干扰时,可能会表现为电感特性,抑制高频能量的泄放,解决方法就是尽量加粗地线,以降低干扰对地阻抗;

2、ADS131E06划分了模拟地(AVSS)和数字地(DGND);

对于没有划分模拟和数字地的ADC芯片,建议按照其datasheet layout guidelines中的方法连接模拟地与数字地;