Other Parts Discussed in Thread: ADS127L11

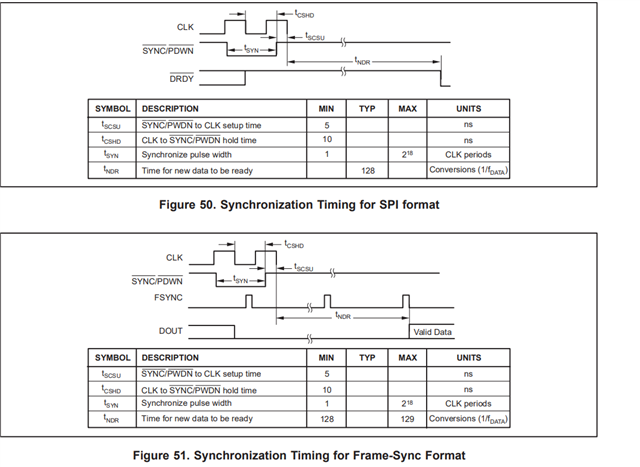

你好!我在查询Datasheet时看到ADS1271可以利用SYNC引脚启动转换。但是实际使用时发现,每次在SYNC引脚给入一个不小于10ns宽度的脉冲信号后大约需要等待67000个CLK周期(实际使用示波器观察到的),DRDY才会产生转换完成下降沿,这个问题怎么解决?请帮忙告知。另外,有没有支持 Daisy-Chain 的24bit具有控制寄存器的同类型ADC推荐,也请告知,谢谢!

我的clk是12.5MHZ,Fs ≈ 24Khz。