Other Parts Discussed in Thread: ADS1299

您好,我是自己设计的采集板,用FPGA驱动,1299的START通过引脚控制。目前,当我的FPGA控制START拉高后,然后发送RDATAC命令后,DRDY始终是高电平,请问这是什么原因?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

上电前您直接将START pin拉高,上电后您用示波器是否可以检测到DRDY信号?

建议您先尝试以上操作以验证ADS1299还可以正常工作;

另外,以下中文FAQ希望对您也有帮助:

我想请问PWDN,和RESET引脚的控制是主控发出的吧

这个要看您硬件电路的设计,这两个管脚是否连接到了主控端的控制管脚,建议外接上拉电阻的,以保证上电后有个默认状态;

上电前将START拉高,您指的是先将START拉高后,然后再拉高PWDN和RESET,也就是根据手册初始化的流程,只不过将拉高START放在最前面?

我说拉高START有DRDY信号,是默认PWDN和RESET已经使能或拉高了

那几个内部电压节点,在测量时需要采集板和主控板进行连接吗?还是说只给采集板供电即可

您说的是VCAP那几个管脚吗?我应为只要给ADS1299供电就可以了

昨晚我将采集板和FPGA主控进行连接,进行了电压测量,Vcap1 = -1.3v;Vcap2 = 0v;Vcap3 =4.3v;Vcap4 = -2.2V

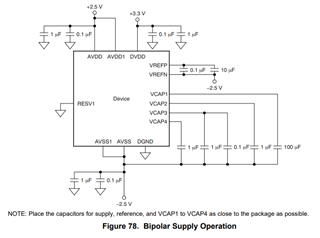

您是怎样供电的?双电源供电吗?各供电电压是多少?您可以附上电路图吗?下面是datasheet推荐的双电源供电电路连接:

我的Vrefp和Vrefn都是-2.5v

这是异常现象,如果都是 -2.5V,那基准电压就是0V了

1.针对PWDN和RESET,如图,两者通过排针和FPGA主控进行连接,

2.我的START信号就是在RESET发出低电平脉冲并拉高后完成寄存器等配置后才拉高

3。针对Vcap那几个管脚的电压,和主控板连接与否会出现不同的电压将采集板和FPGA主控进行连接,进行了电压测量,Vcap1 = -1.3v;Vcap2 = 0v;Vcap3 =4.3v;Vcap4 = -2.2V。不进行连接的话,电压则不对。此外,Vcap4的电压和您给的参考资料不同。

4.采用的是双极性供电,AVDD2.5V,AVSS-2.5V,DVDD3.3V

5.Vrefn Vrefp 电压都是-2.5V,所以基准电压不对,还造成了Vcap4的电压错误