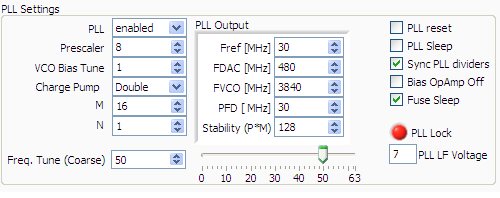

最近在使用DAC3482芯片,使用AD9517提供DACCLK P/N(30M),然后使用3482内部PLL产生480M的DACCLK,相关分频器M=16,N=1,OSTR=30M;另外使用AD9517产生240M时钟信号作为FPGA芯片的时钟输入,在FPGA内部以其为参考时钟,使用IP核产生480M(clk_pll,作为数据产生模块的驱动时钟,因为3482是在DATACLK的上升沿和下降沿均进行数据采样,所以设置为DATACLK的2倍)、240M(DATACLK,输出到3482芯片)、10M(SCLK,配置3482寄存器的串口驱动时钟,输出到3482) 这3个时钟。 FIFO使用双同步源模式,相关的32号寄存器使用默认值,根据DATASHEET第44页的说明,FRAME使用DATACLK的16分频;

刚开始提供DACCLK,DATACLK,SCLK,clk_pll,输入数据位全0,配置完所有寄存器之后拉高TXENABLE信号,输入数据变为正弦信号,同时给SYNC信号一个上升沿用于同步3482内部的PLL。

在以上配置和时序的情况下,每次FIFO都会冲突,复位后还是冲突,请各位朋友帮我分析一下原因,在线等,比较急,谢谢!