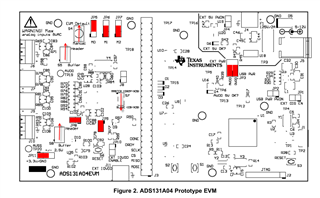

评估板版本:ADS131A04EVM REV-A 非官网最新版本 软件采用:Delta-Sigma ADC EvaluaTIon Software 电脑系统:window 10

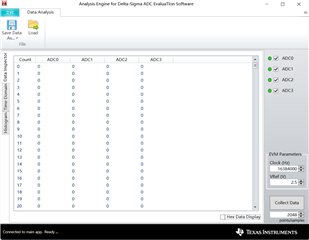

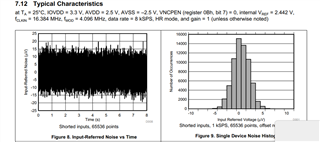

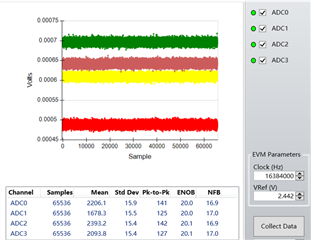

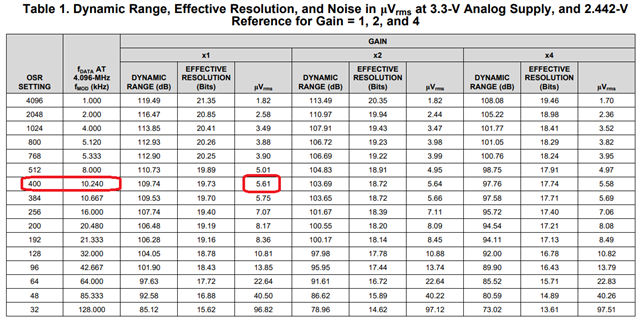

按照用户手册,配置了硬件和软件,可以通讯上,但在ADC输入引脚无论接入什么电压,采集的数据都为0,但是我可以确认供电没问题,寄存器也是按照用户手册默认的。整个评估板模拟供电AVDD为3.3V AVSS为0V

IOVDD为 3.3V ref为2.5V。电压确认没问题。

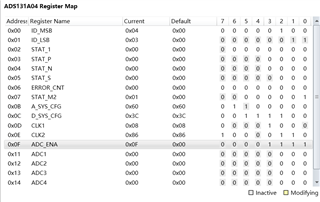

软件通讯上后,我只做了如下操作:1、在软件中发送命令unlock 2、将寄存器ADC_ENA 使能为1,所有ADC通道均使能