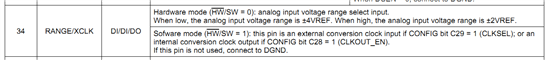

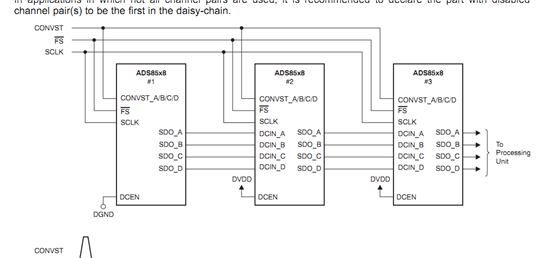

使用两片ADS8568进行16通道同步采样,原理图在附件中,使用的是串行、软件模式。采样速率不高于10KHz,所以输出只用了一个SDO_A。在采样之前对芯片的配置应该是SDI(pin22)和SCLK(pin21)吧,对两个芯片做同样的配置就把这两对脚都接在一起了,不知道这样是否正确?另外datasheet里面对pin34的描述如下所示,pin34在硬件模式下是选择输入范围的

但CONFIG Bit里面对Bit29的描述如下所示

上图标记部分却说这一位在硬件模式有效,如果把这一位置1了,那pin34就是外部转换时钟输入,跟上面的选择输入范围不是冲突了吗?