需求:

使用差分时钟:输入80MHz,

使用CPLL 生成采样率720Mpsp采样信号

JESD使用mode0,单lane速率5.76Gbps,使用8个lane,数据加扰,sysref信号0.2815MHz

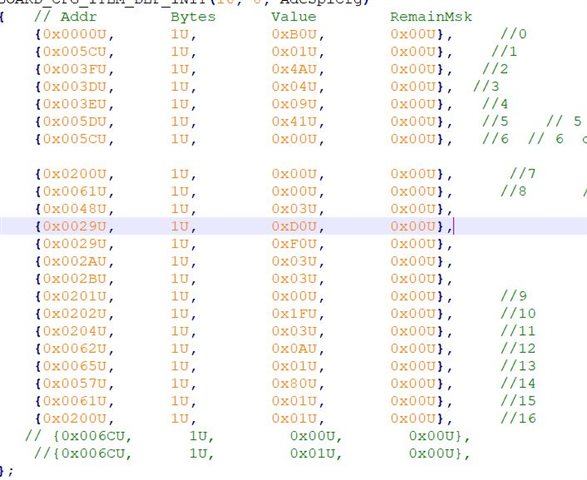

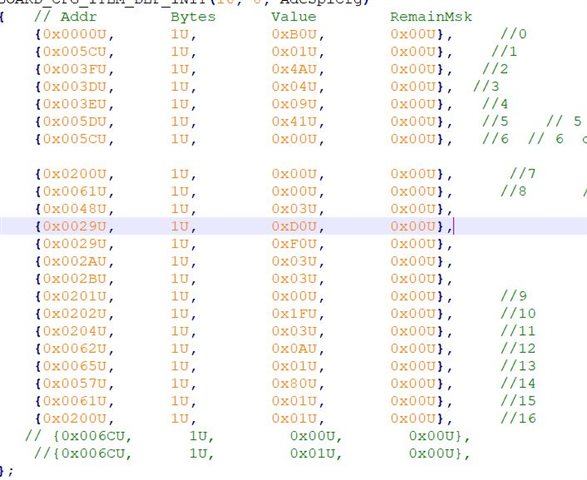

寄存器配置表如下:

第一列为地址,第三列为寄存器写入值

最后的现象如下:

为什么sync信号会周期性拉低

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

需求:

使用差分时钟:输入80MHz,

使用CPLL 生成采样率720Mpsp采样信号

JESD使用mode0,单lane速率5.76Gbps,使用8个lane,数据加扰,sysref信号0.2815MHz

寄存器配置表如下:

第一列为地址,第三列为寄存器写入值

最后的现象如下:

为什么sync信号会周期性拉低

您好,

您咨询的上一个问题,E2E英文工程师已给出答复,您尝试下他给出的寄存器配置,看下是否对这个问题有所启发:

https://e2echina.ti.com/support/data-converters/f/data-converters-forum/496795/adc12qj800-q1