Part Number: ADC32RF42EVM

Other Parts Discussed in Thread: LMK04828, ADC32RF42

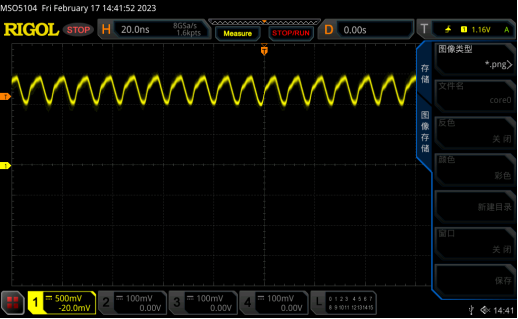

您好,我将ADC32RF42 EVM与xilinx ZC706开发板直接相连,由LMK04828提供时钟(ADC32RF42 EVM上的C409,C410被焊下,C431,C432用焊锡连接),工作模式采用DDC,complex,D=10,LMFS=4841。Linerate=4G,ADC_Fs=1G,Core_clk=100M,GTX_CLK=100M,SYSREF=1.5625M。时钟波形可以正常产生,但是JESD204B时钟无法建链成功----FPGA那端能接收到SYSREF,但SYNC始终是低电平。请问这是什么原因呢?以下是我们测的时钟波形,以及ADC的寄存器配置值:

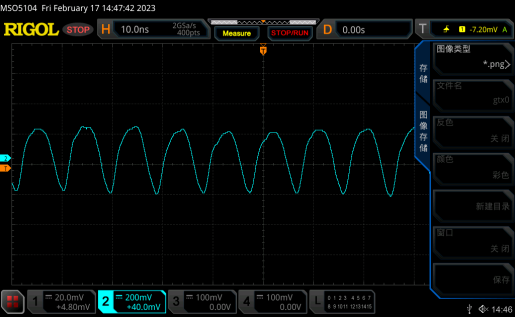

Core_clk=100M---- 串接0欧电阻(LVDS): GTX_clk=100M---串接0.1uF电容(LVDS) : SYSREF_FPGA=1.5625M-------- 串接0欧电阻(LVDS):

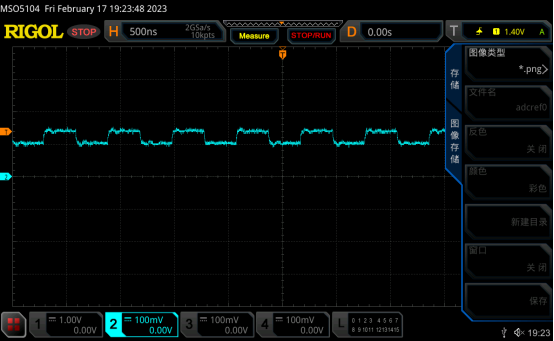

SYSREF_ADC=1.5625M-------- 串接100欧电阻(LVDS)

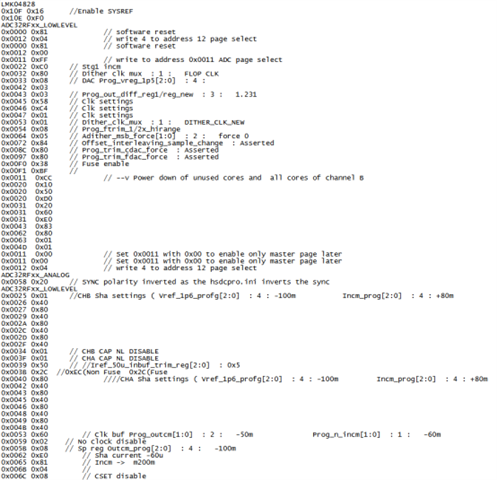

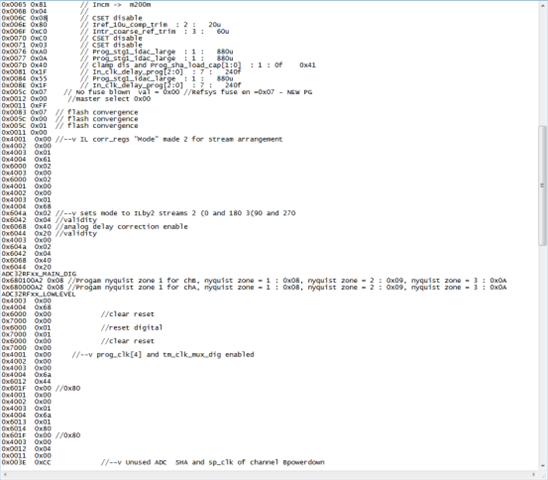

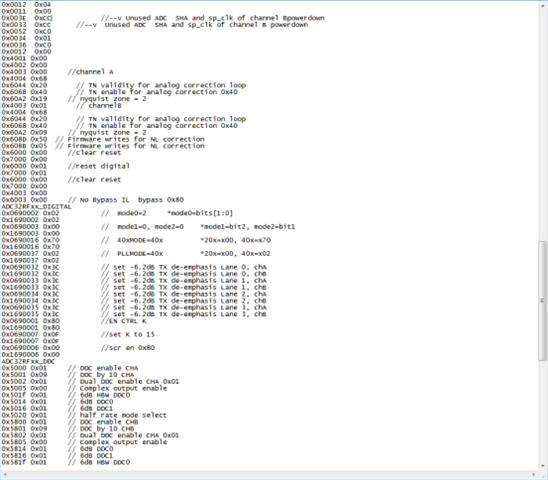

ADC寄存器配置: