Part Number: ADC32RF42EVM

Other Parts Discussed in Thread: ADC32RF42, LMK04828

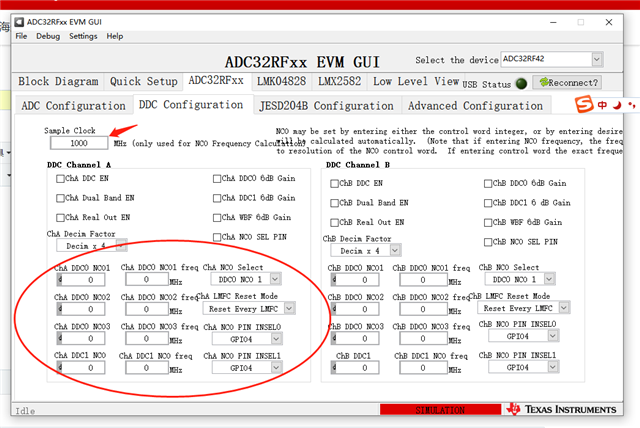

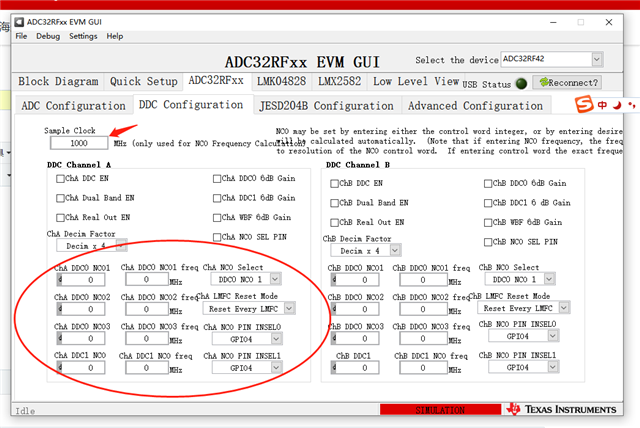

你好,在这GUI界面配置DDC时,我在数据手册一直没找到DDC0 NCO1等相关的配置,NCO的配置是否会影响最后数据的传输与接收?

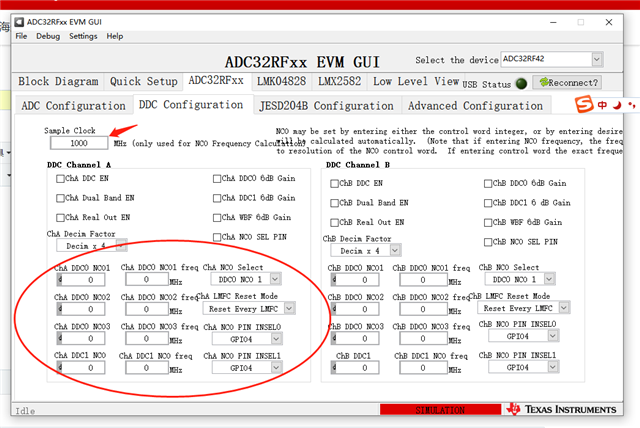

如果影响大的话,在采样时钟设置为1000MHZ时,我要怎么对NCO配置呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADC32RF42EVM

Other Parts Discussed in Thread: ADC32RF42, LMK04828

你好,在这GUI界面配置DDC时,我在数据手册一直没找到DDC0 NCO1等相关的配置,NCO的配置是否会影响最后数据的传输与接收?

如果影响大的话,在采样时钟设置为1000MHZ时,我要怎么对NCO配置呢?

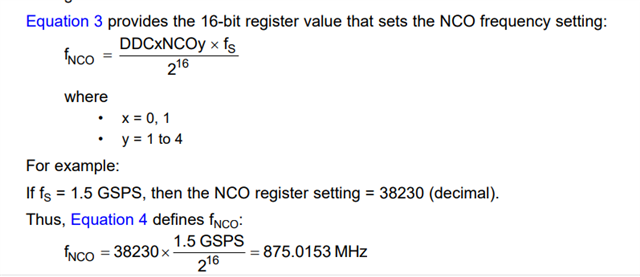

您好,NCO frequency部分可以参考数据手册9.3.4.5 Numerically-Controlled Oscillators (NCOs) and Mixers部分介绍,根据公式3计算NCO频率:

我的问题还没解决,能不能帮我把下面这个问题转到英文论坛?

Hello, we have been debugging ADC32RF42 for nearly a year, but there is still some confusion. I look forward to your help.

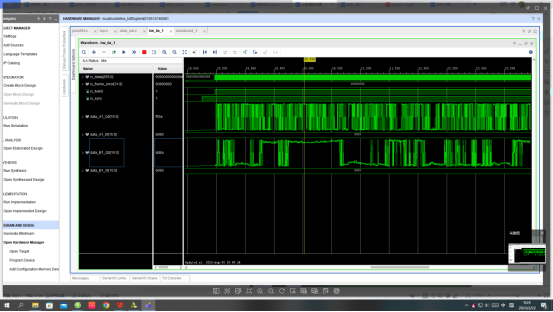

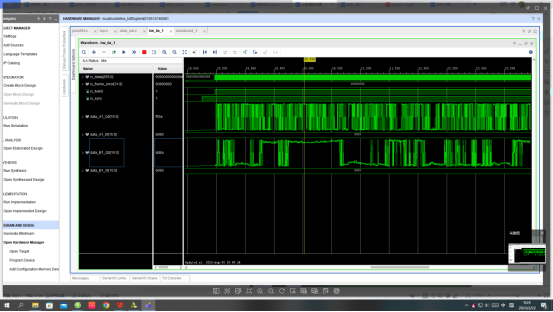

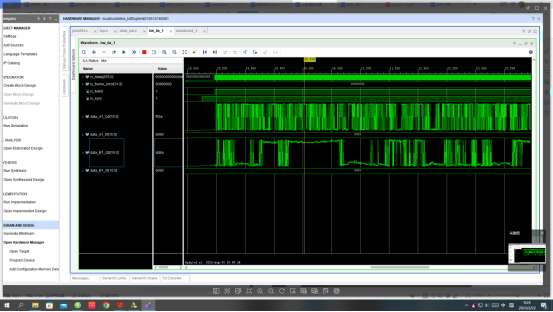

We used ADC32RF42 and LMK04828 chips. Currently, the bypass mode failed to build a link. But the DDC pattern can establish links.

DDC mode uses the dual passband complex 4841 mode, the clock module should have no problems, the download is also the official program. At present, the 1GSPS with sampling rate can normally receive data under the link layer transmission layer and 12bit test mode. However, in the test mode 0/1 of DDC, the data could not be received, and the FPGA end could only see half of the chaotic data when the oscilloscope gave the signal. I don't know what the problem is. DDC configuration interface diagram and vivado upper board diagram are as follows:

好的,我帮您将问题提交到E2E,如有收到答复,我会尽快通知给您。