Part Number: DAC81402

Other Parts Discussed in Thread: DAC81404

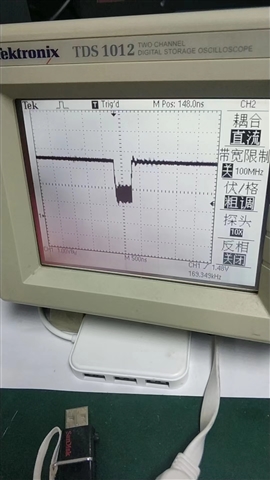

这种情况能识别吗,时钟怎么不太好

这种情况能识别吗,时钟怎么不太好

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

关键是DAC还能识别出波形,请问怎么回事。

如果DAC能够识别,那有可能是测量的问题,您用示波器同一个探头测量其他信号是没问题的吗?DAC能够识别,还可能是DAC能够识别的数字信号阈值范围比较大,而标出的0.3*IOVDD是所有IC都能够100%识别出来的范围。也就是说这个芯片能够识别不代表所有的芯片都能够识别。

还是因为CLK接了上拉电阻的问题?

也可能是上拉电阻的问题,您去掉上拉电阻,测试波形是否有所改善?

是否需要接上拉这要看SCLK的输出接口类型,如果是OC或OD输出接口是需要接上拉的,如果是push-pull接口,则不需要;

另外,输出低电平与输出接口的下管导通电阻有关,如果接口内部下管导通电阻比较大,流过一定的电流就会产生比较大的电压,使得输出低电平偏高。

SYNC信号频率比较低,而SCLK信号频率比较高,它们对PCB layout要求不一样。

您这边是否可以去掉SCLK的上拉电阻,再测试下其波形?

DAC81404是4通道的,而DAC81402是2通道的,我看它们封装是一致的,寄存器也是一致的,应该可以P2P兼容,但是需要您在一个板子上验证一下,我这边没有实际验证。

很高兴上述波形问题是示波器的原因,感谢您的反馈!

DAC81402什么时候能有货

建议您关注DAC81402芯片的产品主页,库存以您登录TI.com后看到的为准,TI会实时更新库存情况。

DAC81402产品主页:https://www.ti.com.cn/product/cn/DAC81402

打开产品主页,点击右上角“立即订购”网页会自动滑动到订购部分,那里会显示库存情况。

关于在线购买问题/订单问题,请您参阅在线订购常见问题解答:https://www.ti.com.cn/zh-cn/ordering-resources/help.html

如果常见问题解答不能解决您的问题,建议您请按照以下方式联系客户支持部门,会有客服为您提供帮助。