Part Number: ADS1294

Other Parts Discussed in Thread: ADS1291

我们的设计采用的是ADS1294芯片前三个通道采集心电信号。基本功能都正常,心电信号采集也正常,但在调试中发现一个现象:就是将导联电极扣脱落放置在桌上的时候,系统电流会比全接信号的时候上升100uA左右,但将导联线保持脱落状态拎起来悬空,系统电流相比全接信号的时候下降100uA左右。比较困惑这到底是什么原因造成的。我能想到的可能的因素是ADS1294芯片中有关导联脱落检测和右腿驱动相关的配置。由此引出,一些有关导联脱落检测配置以及右腿驱动抗干扰的问题想请教:

1.手册中描述LOFF寄存器中COMP_TH的设置的各种等级阈值,对于导联脱落检测具体起到哪些作用,不同的百分比阈值,对于脱落的检测是更灵敏还是更迟钝?在哪种条件下设置哪种阈值更有利?

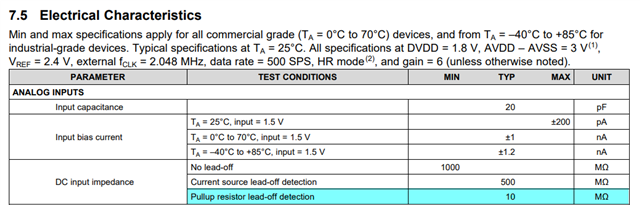

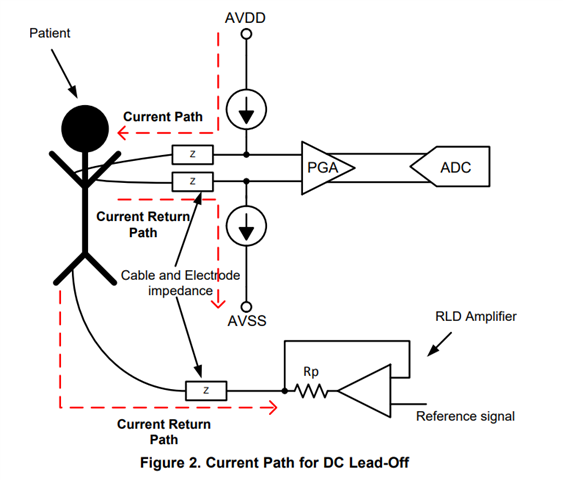

2.我的设计采用的是电流源的直流导联脱落检测模式,相关寄存器配置为LOFF=0x03,LOFF_SENSP=0x07,LOFF_SENSN=0x07,LOFF_FLIP=0x00,CONFIG4=0x02请问这种配置是否正确?这种检测模式和上拉下拉电阻直流导联脱落检测模式相比,哪种更合适,哪种更省电?

3.如果在外围电路不变动的情况下,基于上面的配置,是不是只要将LOFF寄存器中的FLEAD_OFF[1:0]位由11改为01后,就切换到了交流导联脱落检测的模式了?那么在交流导联脱落检测中是否也分别有电流源模式和上拉或下拉电阻器模式?(这部分在手册中介绍的不多)。同时请问交流导联脱落检测和直流导联脱落检测各自的优缺点是什么?一般多用哪种模式?哪种模式更省电一些?

3.我在测试中发现一个现象:如果导联上采集的信号比较稳定,比如正常的心电波形(幅值为2到5mV)的时候,系统功耗电流正常。但是如果某条导联脱落,同时引入了幅值较大的且频率较高的干扰杂波(幅值为10mV以上频率为几百赫兹),这时系统电流会上升约100uA。我将导联脱落检测功能完全关闭,LOFF=0x00,LOFF_SENSP=0x00,LOFF_SENSN=0x00,CONFIG4中的PD_LOFF_COMP=0,但是这个现象仍然必然复现。所以我不明白这是什么原因造成的?是否是芯片内部电路本身就有这个特点,对高频率高幅值的信号进行AD转换时功耗必然会提高?还是我在寄存器配置时有什么不正确造成的。

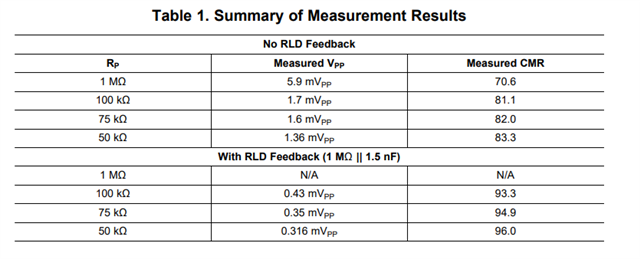

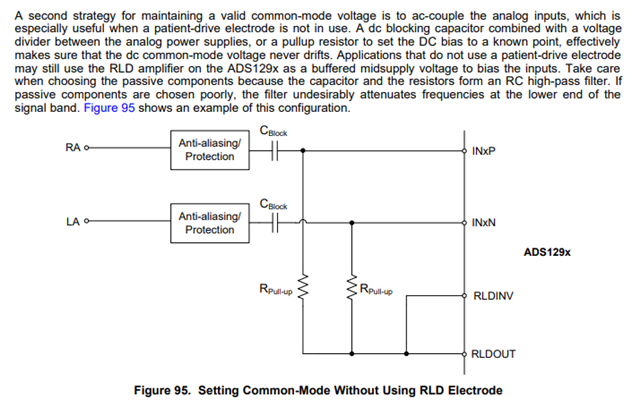

4.由此引出右腿驱动相关配置的问题。我们的设计目标就是传统的十二导模式,右腿RL电极就是起到抗干扰作用就可,不需要对其上的信号进行检测。我们外围电路也是和您们官方开发测试板的接法一致。但是看到手册中介绍了各种右腿驱动的使用方式,外接方式,测量方式,不同的寄存器配置,我有些混乱,不知道哪种才是我们适合的配置方法。比如RLD_SENS,RLD_SENSN,CONFIG3这些寄存器的配置方法。我希望RL电极可以起到抗干扰的作用,那么我理解RL电极应该在内部反馈给各个通道的运放才能起消除共模干扰的效果,所以我把寄存器RLD_SENSP和寄存器RLD_SENSN所有位置1,同时寄存器CONFIG3中RLDREF_INT位=1,/PD_RLD位=1启用RLD缓冲器。但是我又不是要测量RLD的信号,所以把寄存器CONFIG3中RLD_MEAS位=0,RLD_LOFF_SENS位=0。我用这种配置实际测试各个通道信号是正常的。但是感觉好像概念上有些混乱。我又尝试将RLD_SENSP=0,RLD_SENSN=0,实验效果和刚才相同,没有看到什么区别。

5.在4中描述的两种配置时,将RL电极处于导联脱落状态,发现读取到的正信号导联脱落LOFF_STATP寄存中,我所启用通道的对应位都被置1了,负信号导联脱落LOFF_STATN寄存器中对应位都为0。于是我借用此特点用来判断RL是否脱落,而不使用读取CONFIG3寄存器中的RLD_STAT位方法。但是不敢确定这种试用方法是否正确。

所以想请教应该如何配置是符合我们设计预期的。

6.下面是我当前的各个寄存器的配置参数,请看是否正确:

CONFIG1=0x06

CONFIG2=0x32

CONFIG3=0xCC

LOFF=0x03

CH1SET=0x00

CH2SET=0x00

CH3SET=0x00

CH4SET=0x80

RLD_SENSP=0x07

RLD_SENSN=0x07

LOFF_SENSP=0x07

LOFF_SENSN=0x07

LOFF_FLIP=0x00

GPIO=0x0F

PACE=0x00

RESP=0x00

CONFIG4=0x02

WCT1=0x0B

WCT2=0xC2

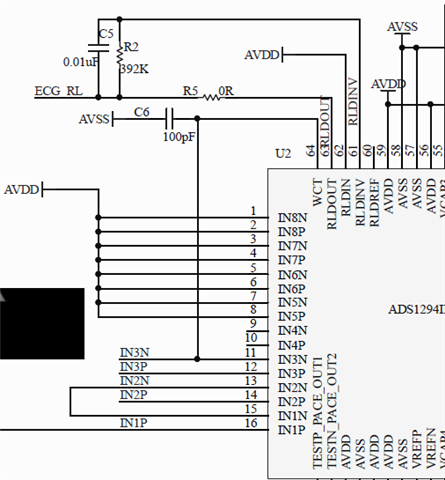

下图是我们外围连接图