Part Number: ADS4222

我现在正使用ADS4222,但碰到几个问题

1:硬件配置SEN引脚未起作用;SEN引脚和芯片电源上电,同时到达预设值,SEN引脚的电压也满足3/8VCC±50mv;若用跳线将SEN接入FPGA,采用软件配置的方式,可以配置。

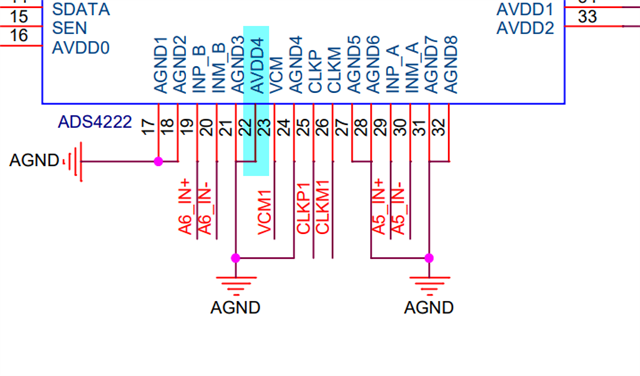

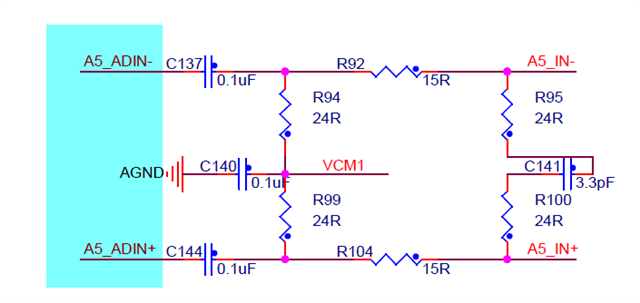

2:输入悬空状态下,采集到的数据偏负半轴。外部数据通过0.1uf的电容耦合进入ADC,将耦合电容取下,即外部数据无法输入的情况下,采集到的数据任然在0~负130之间;测量VCM值为0.966,超过了规定,不知道是否影响

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS4222

我现在正使用ADS4222,但碰到几个问题

1:硬件配置SEN引脚未起作用;SEN引脚和芯片电源上电,同时到达预设值,SEN引脚的电压也满足3/8VCC±50mv;若用跳线将SEN接入FPGA,采用软件配置的方式,可以配置。

2:输入悬空状态下,采集到的数据偏负半轴。外部数据通过0.1uf的电容耦合进入ADC,将耦合电容取下,即外部数据无法输入的情况下,采集到的数据任然在0~负130之间;测量VCM值为0.966,超过了规定,不知道是否影响

即外部数据无法输入的情况下,采集到的数据任然在0~负130之间;

这里您采集到的二进制码是多少?

将RST拉高后,输出信号电平值为0~1.8V

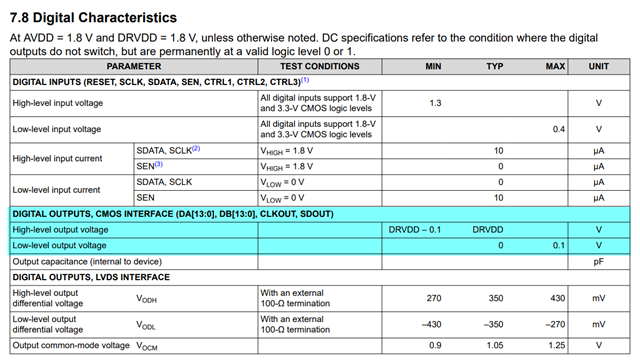

是的,1.8V供电的话,输出高低电平如下截图:

刚开始没注意到您附电路图了,现在看您的电路图,22脚AVDD是不是接错了?查看下PCB是否接错了?或量一下AVDD电压是否正常?

好的;

1、reset pin 您实测一直是高电平吗?您可以用示波器监测一下reset pin 吗?

RESET pin 您是否接上拉至高电平?我不确定RESET pin 是否需要外部接上拉,即是否上电启动时就需要是高电平而不是上电后再拉至高电平,因此您若外部没有接上拉,您可以尝试外接上拉至电源吗?

2、

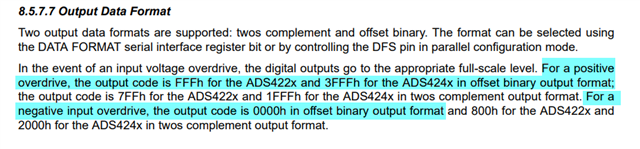

2:对的,上述采集code 十进制数值。原始采集到的值为06ff、06fd、06fc、06fa、或者0800、0801等;原始值很规律,就在这几个值之间变化

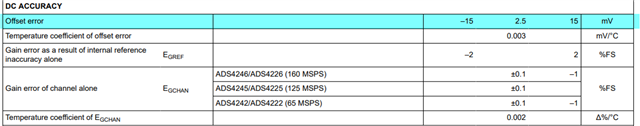

您这里的意思是说输出为什么不是0V吗?ADC它是存在输入失调电压的,典型值是2.5mV,最大值是±15mV,

ADS4222是12bit ADC,其输出是12bit,如果您使用的是offset 输出格式,那么输出值是在其输入失调电压范围内的。

如果您是使用的二进制

1、感谢您的反馈。那就是需要外部接上拉,以在设备上电的时候检测RESET pin 电平状态配置其工作方式。如果不硬件上拉,上电过程中 RESET pin电平状态不正确,不能进入期望的工作方式。

2、在ADS4222的增益是0dB时,满幅输入范围FS是2V,即-1V~+1V,输出code 分别对应000h ~FFFh,1LSB=2V/(2^12-1)=488.4uV 0V就是7FFh

801h转换为十进制数是2,乘以1LSB就是对应的输入模拟电压为2*488.4uV约为1mV

6ffh 转换为十进制数是-256,乘以1LSB就是对应的输入模拟电压为-125mV,

06ff、06fd、06fc、06fa 这几个值偏大了一些,ADS4222是12bit分辨率,不知道您为什么用4位十六进制数表示?不知道您这里采集数据是否有误?

2:对的,上述采集code 十进制数值。原始采集到的值为06ff、06fd、06fc、06fa、或者0800、0801等;原始值很规律,就在这几个值之间变化

如果输出值是它们之间变化的,那么变化值Δ就是测量的噪声,所以请考虑引入噪声的参数,比如供电电压的纹波或噪声、时钟jitter、PCB layout 等,这些方便可能会引入噪声。

感谢您的回复,关于噪声这块,我补充几个情况,

1:电路板上设计有两块ADS4222,共计4个ADC通道,相同情况下(输入悬空),我测试了3块板子(这里简称A,B,C板),A板和B板有两个通道输出数据保持为800,801,大约是1~3mv(两个通道位于不同的ADC上),C板只有一个通道输出数据保持为800,801,大约是1~3mv,其余通道输出情况如上文所述(原始采集到的值为06ff、06fd、06fc、06fa、或者0800、0801等原始值很规律,就在这几个值之间变化)。

2:两片ADC采用同一个电源供电,时钟是同一个时钟buff提供的两个时钟。4个模拟通道PCB layout是一样的。

3:FPGA采样并行io电平采用200MHZ,ADS4222的时钟频率为25MHZ。

另外想请教一下,数据手册上没有看到ADS4222的COMS输出模式下的内部阻抗,与FPGA之间,应该串多大的电阻已做阻抗匹配

1、您描述的“(输入悬空)”我默认是指Ax_ADCIN± 这里悬空的。

2、这里主要考虑的是电源线、时钟线在走线过程中也会受到周围高频信号的干扰,虽然源是一样的,但是分支可能受到不同的干扰。

3、CMOS输出接口输出阻抗非常小,下面链接是EVM板提供了设计文件,您可以参照其原理图串联22Ω电阻: