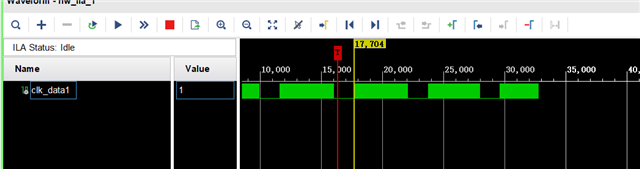

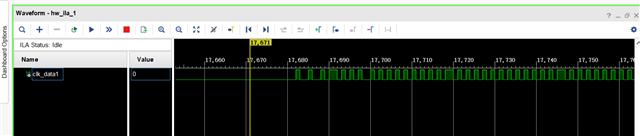

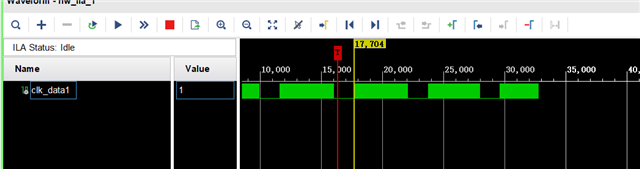

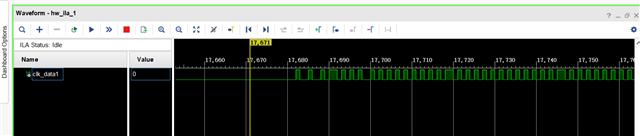

你好,我在FPGA接收ADC的DCLKP和DCLKM引脚(也即接收DCLK信号),用ILA抓出来的波形如下图所示,可以发现DCLK信号会出现规律性持续为0,且在有DCLK信号的时候,他的波形并不是恒定的(即频率不稳定,导致脉冲波形时而宽时而窄),请问是怎么回事?

PS:我用示波器探测DCLKP、DCLKM引脚,探测出来是一个频率基本稳定的类似方波的波形

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,我在FPGA接收ADC的DCLKP和DCLKM引脚(也即接收DCLK信号),用ILA抓出来的波形如下图所示,可以发现DCLK信号会出现规律性持续为0,且在有DCLK信号的时候,他的波形并不是恒定的(即频率不稳定,导致脉冲波形时而宽时而窄),请问是怎么回事?

PS:我用示波器探测DCLKP、DCLKM引脚,探测出来是一个频率基本稳定的类似方波的波形

您好,我可能没明白您的意思,您的意思是用ILA抓出来的波形DCLK信号会出现规律性持续为0,即频率不稳定。但是用示波器测DCLKP、DCLKM就是频率稳定 的方波图形是吗?

那用示波器测量DCLK(FPGA内部实现差分转单端)的波形怎么样?

因为我觉得这个问题很奇怪,不是说使用不同的测试仪器导致波形或占空比的稳定与否。 那针对ILA或示波器,我想就测试同样的信号,比如同时测量差分信号,或者同时测量差分转单端的信号,比较下是否一致?