Part Number: ADC12DJ5200RF

Other Parts Discussed in Thread: ADC12DJ3200

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADC12DJ5200RF

Other Parts Discussed in Thread: ADC12DJ3200

看下下面链接中帖子的回复是否对您有帮助:

您好,我们按照2篇帖子中的内容进行了验证,仍然无法解决,目前仍然无法解决问题,请问还有其他方法吗?非常感谢您。

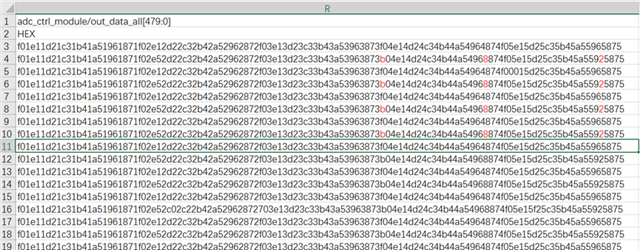

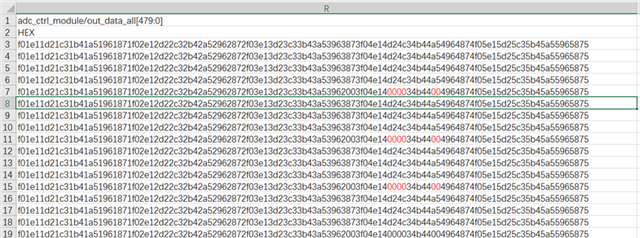

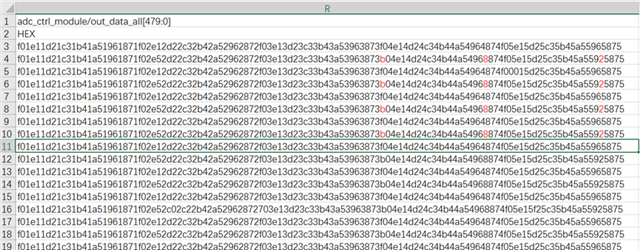

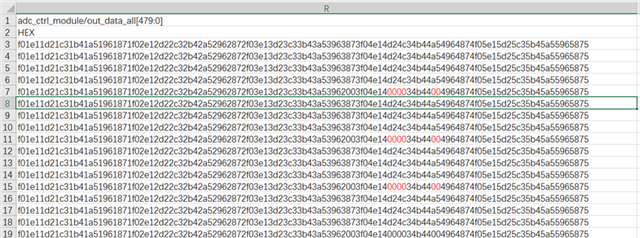

这是我们的ADC配置,该配置在8GSPS采样率下是可以正常运行的。

0:dout<=24'h0000B0; ///***///进行软复位 之后延迟100ms

//时钟50MHz 20ns * 5000 = 100 ms

4999: dout<=24'h002B15;

5000: dout<=24'h02A230;

5001: dout<=24'h020000; ///***///清除 JESD_EN (始终在 CAL_EN 之前)

5002: dout<=24'h006100; ///***///清除 CAL_EN (始终位于 JESD_EN 之后)

5003:dout<=24'h020101;//jmode

5004:dout<=24'h020203;//km

5005:dout<=24'h020301; //设置为 非JSYNC_N模式

5006:dout<=24'h020400; //00 01 Scrambler disabled

5007:dout<=24'h020505; //设置JTEST

5008:dout<=24'h0030FF; //设置A通道的量程

5009:dout<=24'h0031FF;

5010:dout<=24'h0032FF;//设置B通道的量程

5011:dout<=24'h0033FF;

5012:dout<=24'h002920;

5013:dout<=24'h002960;

5014:dout<=24'h002970; ////// 将串行器预加重设置为3 第三步:0111_0000 将此位设置为放大SYSREF 滤波 状态(影响SYSREF_POS)

5015:dout<=24'h002965; //第四步:设置要使用的SYSREF的延迟,根据SYSREF_POS返回的结果进行设置。将该字段设置为0以使用SYSREF校准。

5021:dout<=24'h006201; //校准配置 第0号寄存器 其实可以不用设置,使用默认配置就行,默认 不使能背景偏置校准 , 默认使用foreground校准

5137:dout<=24'h02C11F; //Alarm Status Register

5138:dout<=24'h02C200; //Alarm Mask Register

5139: dout<=24'h006101; ///***///设置 CAL_EN (始终在 JESD_EN 之前)

5140: dout<=24'h020001; ///***///设置 JESD_EN (始终在 CAL_EN 之后)

5142: dout<=24'h006C00; ///***///将 CAL_SOFT_TRIG 设置为低电平以复位校准状态机

5143: dout<=24'h006C01;

我咨询的工程师也分析说是信号完整性的问题。您可以在ADC侧实施serdes的预加重设置。

通过用0x01或0x02、0x03等值编程寄存器地址0x48,查看问题是否消失。

在FPGA方面,您可以使用均衡设置,看看它是否有助于解决这个问题。

To me this looks like signal integrity issue. The customer can play with Pre-emphasis setting on the ADC side for serdes.

By programming the register address 0x48 with value of 0x01 or 0x02,0x03 and so on and see if the issue goes away.

On the FPGA side they can play with equalization setting and see if it helps with the issue.

得到的回复:

如果通过更改预加重设置解决了问题,则确认是信号完整性问题。FPGA上的均衡设置是否也进行了调整?

如果没有,我建议在FPGA上对所有选项进行扫频预加重设置与均衡,并查看哪些设置有效。

如果你在ADC和FPGA方面没有得到稳定的设置。否则另一种选择是在考虑信号完整性的情况下重新制作电路板。

If the problem was solved when by changing the pre-emphasis settings it confirms signal integrity issue. Was equalization setting on the FPGA also adjusted?

If not i would suggest sweep pre-emphasis setting vs equalization on the FPGA for all the option and see which settings works.

if you don't get a stable setting on the ADC and FPGA side. Otherwise the other option would be to re do the board with signal integrity in mind.

该模式显示周期性重复的跳跃。基于这一现象,我们可以消除信号完整性理论。从最新的三角波模式来看,问题似乎在传输层。(如何从JESD信道收集样本并进行通道化)。您可以尝试传输层测试模式,并检查传输层的输出模式是否如预期?

The pattern is displaying jumps which getting repeated periodically. Based on this phenomenal we can eliminate the signal integrity theory. Looking at the latest pattern of triangle wave, The issue seems to be in transport layer.( How samples are collected from JESD lanes and channelized). Can you ask customer to try the transport layer test pattern and check if the output pattern from transport layer is as expected.