Hello, lvds signal was not generated when afe5818 test mode was used to generate LVDS signal. And what registers need to be configured when collecting signals. Thanks for your answer

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

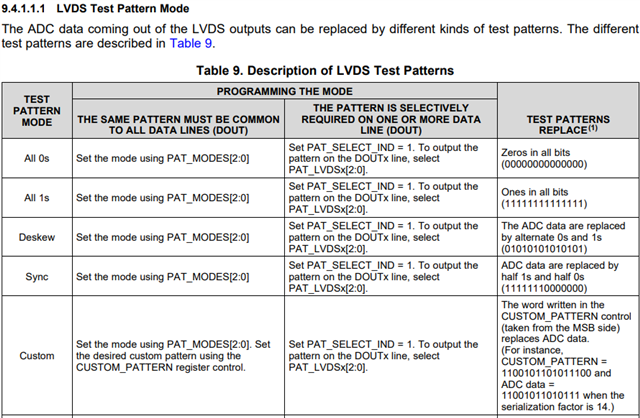

您好,我们可以直接使用中文沟通。LVDS test pattern都很多类型,您配置的是哪种输出模式?

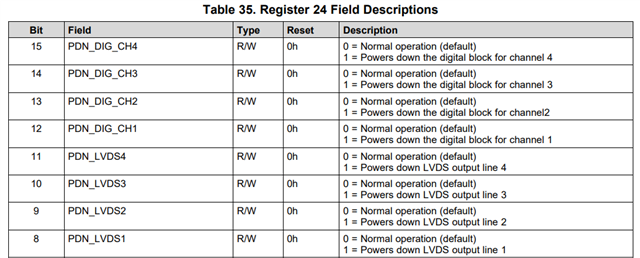

您好,可能和寄存器的配置有关,可能输出power down了,比如register 24可以enable output或者power down output。

Register 4,register21,register 23,24,33,35,36,45,47,48,57,59,60 这几个寄存器都是可以使能LVDS输出 或者power down状态,以及输出pattern类型的配置。

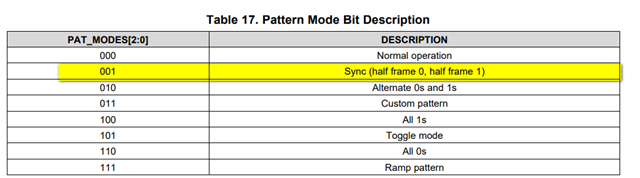

除了PAT_SELECT_IND=0,那register 2的bit[9:7]需要配置输出类型,比如您配置sync模式,那么PAT_MODES[2:0]需要配置为001.

另外,register 2的bit6也要配置为1,enable pattern generated。

您好,配置的是sync,应该是一半帧是高电平,一半帧是低电平,duty cycle是50%,您的波形ducy cycle好像不太对。

这是按照上述配置得到的输出是吗?

初始化以及上电时序是满足datasheet中10.4 Initialization Set Up以及Figure107的上电时序吗。可以用示波器测量下时序。

合理的上电时序是寄存器正确读写的基础。