Other Parts Discussed in Thread: ADS131A04, THP210

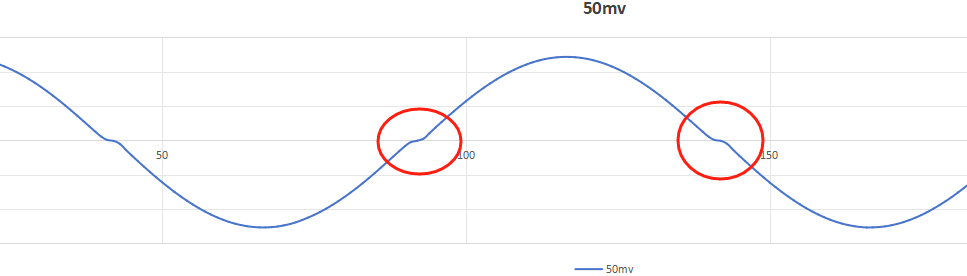

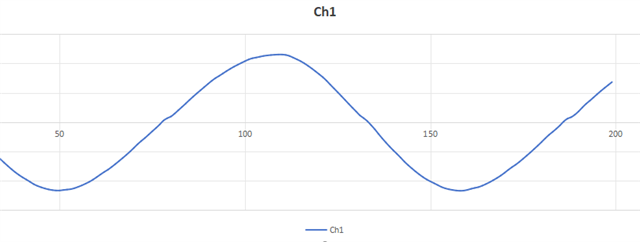

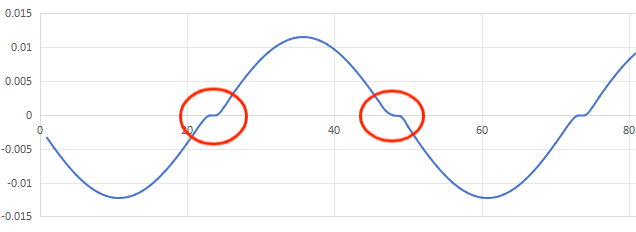

E08通道输入50mv差分信号,正弦波,e08采样率1k,信号频率10hz,数据转换出来的波形如上图,在过零点的时候都有像台阶一样的数据重复出现,请问有遇到过这种情况的吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

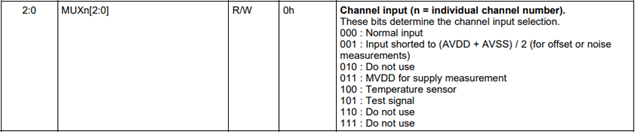

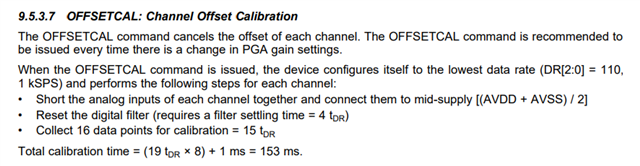

按照数据手册,我将8个通道的引脚都接到了(AVDD+AVSS)/2大约1.65V,然后在程序初始化的时候发送了OFFSETCAL命令。又发送了RESET命令,下面我就正常采样了,各通道上来的数据在372mv-466mv。我又把各通道断开,再接上正弦信号,还是有图上那种偏差的数据,请问我哪里没操作正确。

Collect 16 data points for calibration = 15 tDR

Total calibration time = (19 tDR × 8) + 1 ms = 153 ms.

数据手册上这两句我具体要如何操作?

E08通道输入50mv差分信号

输入共模电压是多少?是否满足datasheet 要求?

AVDD 您是使用3.3V供电是吗?增益设置多少?

按照数据手册,我将8个通道的引脚都接到了(AVDD+AVSS)/2大约1.65V,然后在程序初始化的时候发送了OFFSETCAL命令。又发送了RESET命令,下面我就正常采样了,各通道上来的数据在372mv-466mv

也就是说共模电压1.65V,差分输入为0 的时候,您采集电压是372mv-466mv?这个失调电压有些大呀,您测量供电电压、参考电压是稳定的吗,纹波大不大?

您是不是已经验证了寄存器可以正确读写,即写入后可以正确读出来?您可以附上寄存器配置吗?fault寄存器值是否有异常?

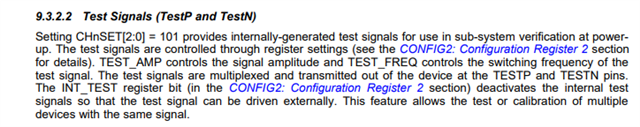

或者您使用 内部测试信号,采样电压是多少?

或配置MUX寄存器,采集电压是多少,这样可以排除外部输入电路的影响。

关于OFFSETCAL,在发送OFFSETCAL命令之前,您需要将START引脚拉高或发送START命令以启动AD转换。

Collect 16 data points for calibration = 15 tDR

Total calibration time = (19 tDR × 8) + 1 ms = 153 ms.

数据手册上这两句我具体要如何操作?

这是设备自动执行的:

供电电压和参考电压稳定的,寄存器可以正常读写,fault无异常。

ADS13_WRITE_CMD(ADS131E0X_RESET_COMMAND); //RESET ADS131

delay_ms(100);

ADS13_WRITE_CMD(ADS131E0X_SDATAC_COMMAND);

delay_ms(100);

ADS13_WRITE_CMD(ADS131E0X_OFFSETCAL_COMMAND);

delay_ms(100);

ADS13_WRITE_CMD(ADS131E0X_RESET_COMMAND);

delay_ms(100);

ID = ADS13_RREG(ADS131E0X_ID); //D2

ADS13_WREG(CONFIG1, 0X96); //110 24-bit output 1ksps

delay_ms(100);

ADS13_WREG(CONFIG3, 0X40); //VREF is set to 2.5 V

//ADS13_WREG(CONFIG3, 0XC0);

delay_ms(100);

//check the REGS

C1 = ADS13_RREG(CONFIG1); //96

delay_ms(100);

C2 = ADS13_RREG(CONFIG2); //E0

delay_ms(100);

C3 = ADS13_RREG(CONFIG3); //40

delay_ms(100);

FA = ADS13_RREG(FAULT); //00

delay_ms(100);

用的默认增益,没有额外设置,所以我就只在初始化里面发送一次OFFSETCAL指令。又发一次reset是因为之前不确定DS文件里说的reset digital filter是硬件复位还是软件复位,问了一下在线客服,说程序里复位,我就加了一次reset命令。

刚刚我把延时改成200ms,去掉了最后一次reset,CHnSET配置成0x11,把所有模拟输入通道还是接到AVDD,取出来的值,依然是几十个mv。

我现在不方便采集内部测试信号,因为设计PCB的时候直接在引脚上把TESTN和TESTP都接AVDD了,断不开。

请问还有其他方式吗?

测得的信号就是50mv基本上没有图片上那种台阶,

此时使用失调电压校准命令了吗?不使用的话,测量结果怎样?

供电电压和参考电压稳定的,

您是用示波器测量的吗?具体纹波多少?

软件上关闭与否为什么会对其他通道采集信号产生影响呢?

不能悬空是为了避免耦合管脚周围的电磁干扰;接AVDD 且 power down的话我认为是为了避免AVDD纹波内部串扰其他通道。总之,要按照datasheet 说明连接。

我如果只用5025为E08提供外部参考电压,负载会把2.5V拉低到1V左右,加上OP运放就能稳定输出2.5V,这个是为什么啊?

外部参考电压还有其他负载吗?如果有的话,看下参考电压的驱动能力是否满足。

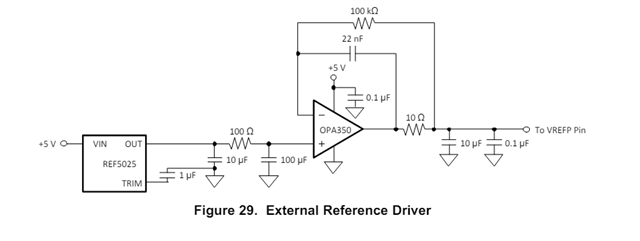

E08的参考电压是建议加buffer 驱动的,如下datasheet 示例截图:

此时使用失调电压校准命令了吗?不使用的话,测量结果怎样?

此时使用了OFFSETCAL命令,同时CHnSET=0x90关闭了1-7通道,因为我只给8通加前端模拟电路了。

如果去掉OFFSET命令,但依然关闭其他不用的通道,此时对采集出来的波形没有影响;

但是如果把CHnSET配置也去掉,即软件上不关闭其他不用的通道,采集出来的波形,台阶就很明显了,与最初图片上波形一样。

您是用示波器测量的吗?具体纹波多少?

电压是用万用表测量的。用示波器看纹波,粗略测量纹波电压峰峰值在80mv,用的长线地。

外部参考电压还有其他负载吗?如果

5025没有其他负载,一开始是5025的输出直接就给E08了,然后运行一阵,就把电压拉到1V左右,加上运放就稳了。

看您采集其他电压基本是正确的,只是误差有点大,我理解应该是输出失调造成的,所以现在想找出输出失调是什么原因造成的。

刚刚就直接配置成连接AVDD+AVSS / 2,读出来的值就是几十个mv

您现在是差分输入为0,共模输入(AVDD+AVSS) / 2,采集电压是几十个mV是吗?

用示波器看纹波,粗略测量纹波电压峰峰值在80mv,

参考电压纹波也这么大吗?

纹波频率是多少,您可以用纹波的幅值和频率,根据PSRR参数估算供电纹波对输出失调的影响。

但不管怎样几十mV的输出失调确实比较大,您可以附上电路图吗?我看下电路接线是否存在问题;

另外,您测试几块板子是这种现象?可以多测试几块板子吗以排除焊接问题;

也请确认所使用 ADS131E08进货渠道,最终进货来源是否为TI?

AVSS与DGND需要等电位,因此需要单点连接,您是否进行了单点连接?

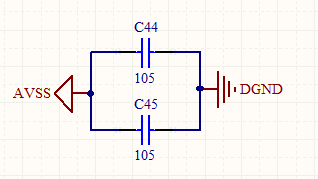

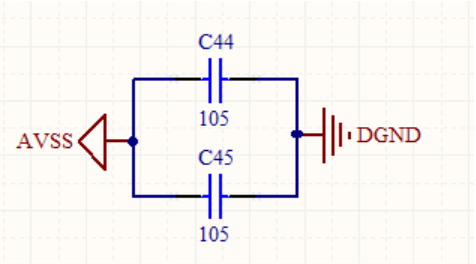

这个忘体现在原理图中了,AVSS和DGND之间有并连两个1UF电容。

建议差分电容C35应至少比共模电容(C33 和C34)高出一个数量级(10x)

我将C35换成了1uf电容

TEST管脚需要经10k电阻接AVDD:

这个再改版会加上去

关于集成了运放管脚,不使用的话可以悬空,但需要power down:

运放脚之前配置CONFIG3=0x40,已经powerdown了。

现在就把差分电容改为1UF,又取了几组数据,5mv的差分信号送进去,还会能看到一点台阶现象。

这样不行,这样低频信号还是没有共地,建议0Ω电阻单点连接。更多信息见下面FAQ:

[FAQ] PCB Layout Guidelines and Grounding Recommendations for High-Resolution ADCs

现在就把差分电容改为1UF,又取了几组数据,5mv的差分信号送进去,还会能看到一点台阶现象。

很高兴有了改善。

你好,还是需要继续咨询上述现象出现的问题。

现在我的8个通道都有前置差分电路,在程序中CHnSET寄存器默认配置,各通道处于正常采集状态,然后给第8通道加12.5mv,10hz的差分信号,采集波形如下

可以看到现象很明显。

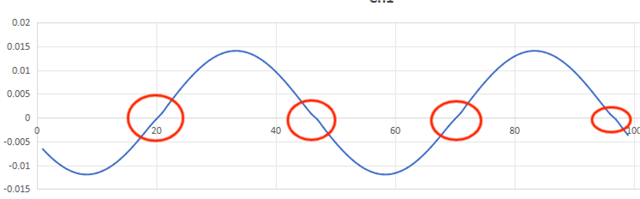

如果在程序中,把其余7个通道关闭,即

ADS13_WREG(CH1SET, 0X90);

ADS13_WREG(CH2SET, 0X90);

ADS13_WREG(CH3SET, 0X90);

ADS13_WREG(CH4SET, 0X90);

ADS13_WREG(CH5SET, 0X90);

ADS13_WREG(CH6SET, 0X90);

ADS13_WREG(CH7SET, 0X90);

第8通道输入同样12.5mv,10hz信号,输出如下图

可以看到现象不是很明显了,但是还是存在的。请问这种如何解释。以及剩下的这点现象如何继续消除。

我之前用过ADS131A04,原理图除了AD部分,电源系统及采样前置电路都是一样的,但是A04就没发现这种情况。请问还有什么地方可能影响信号吗?

THP210输出阻抗很小,应该不是输出阻抗的问题;

我用ADS131A04采0.8mv小信号,波形就挺好

前置差分电路和电源部分都相同,用ADS131E08采集信号,就有之前的台阶现象。

PCB layout 也一样吗?如果一样的话,我需要对比下这两款芯片的性能。

您示波器测量ADC 输入管脚处波形是怎样的?我想输出与输入波形对比下

异常时,您可以用示波器测量ADC 输入管脚处波形是怎样的?然后与输出波形做对比,看下是否前端电路引入的失真