Part Number: ADC083000

当前使用FPGA芯片控制ADC083000工作,FPGA输出的时钟是600Mhz,使用DDR模式接收ADC输出的数据。

当前使用的是交流耦合模式。然后通过外部扩展模式(SPI接口)配置ADC083000。当前的状态是,通过SPI接口配置,ADC芯片能进入测试模式。这时FPGA能正确接收到ADC输出的测试数据。但是当模式切回正常的采样模式的时候,FPGA接收到的数据为全FF,且OR一直显示为高。但是此时模拟输入没有加入激励信号。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

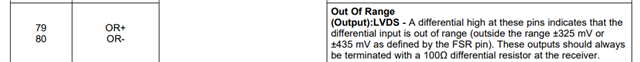

OR是高电平说明输入超出输入范围了:

但是此时模拟输入没有加入激励信号。

没有加入激励信号是悬空吗?模拟输入一般不建议悬空,会耦合周围的电磁干扰。

这里建议您将模拟输入端输入有效信号,看是否可以正确采集?

模拟输入端接有效信号后依然不能正确采集。

不能正确采集具体现象是什么?输出还是全F吗?此时OR状态是什么?

请给出下面问题的答复:

“输入幅度在200mv左右”是指上图中QADC_IN_P/QADC_IN_N处的差分幅值吗?还是输入耦合电容之前的电压?VCMO是否接地?

QADC_IN_P/QADC_IN_N是连接的ADC083000 输入管脚VIN+/VIN-吗?

但是当模式切回正常的采样模式的时候,FPGA接收到的数据为全FF,且OR一直显示为高。但是此时模拟输入没有加入激励信号。

此时您有没有检测calrun管脚的状态?此时是低电平吗?因为低电平表示校准完成。如果在校准过程中,使用内部模拟开关从内部转换器断开模拟输入信号,且SPI接口不处于有效状态(除了写入校准位以启动校准过程外)