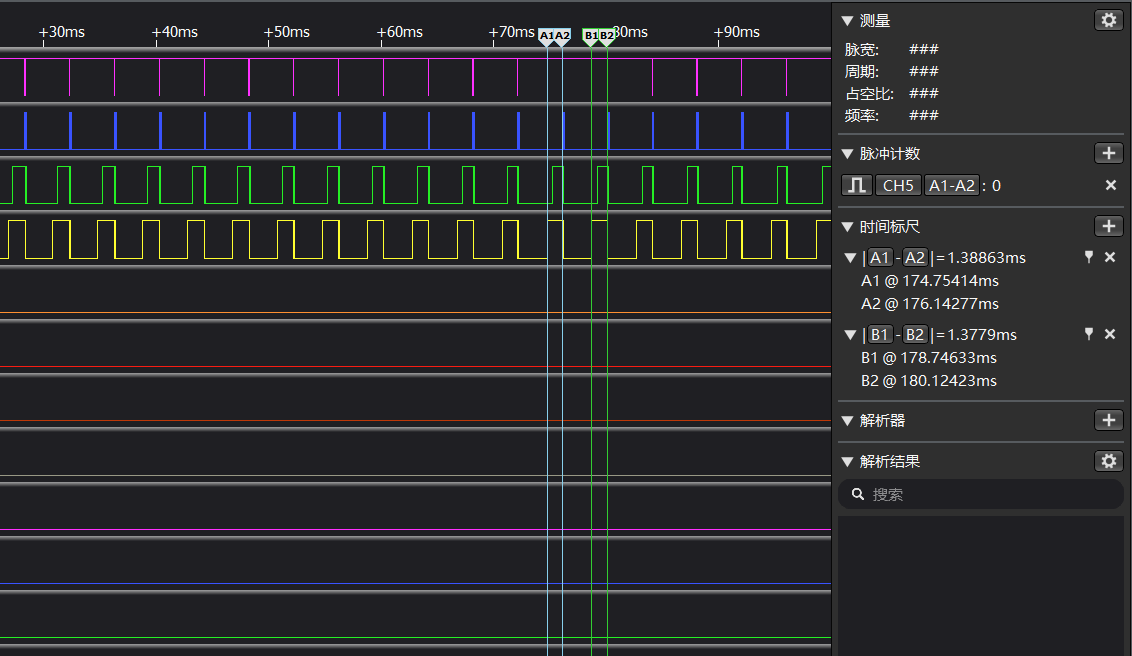

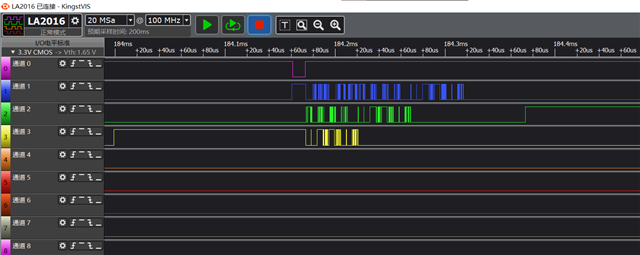

使用逻辑分析仪读取链上每片数据输出,发现在片与片的标志位没对齐的时候发生数据读出错误,如下图所示(通道0:DRDY、通道1:菊链上1st输出、通道3:菊链上2st输出、通道3:菊链上3st输出)

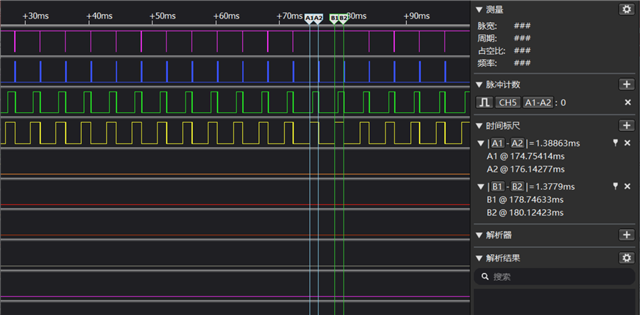

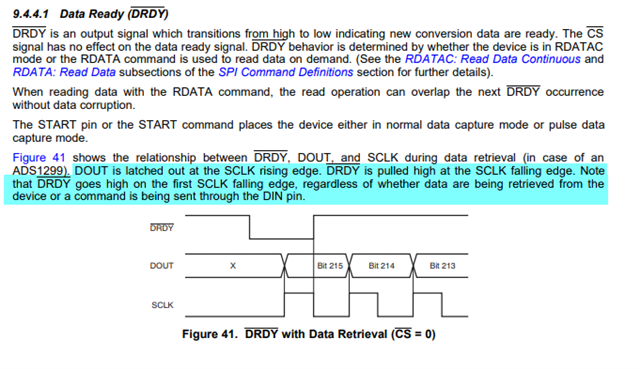

每组数据传输结束后,在数据准备时间内Dout的波形占空比会随数据传输依次降低。如下图所示,通道3,在A1-A2期间Dout反转为高电平,保持1.3886ms后开始输出,到下一组时Dout反转为高电平,保持1.3779ms后开始数据输出。

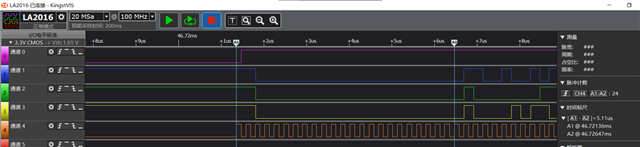

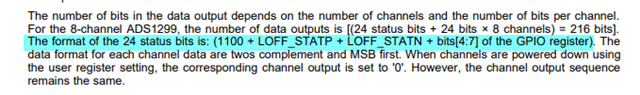

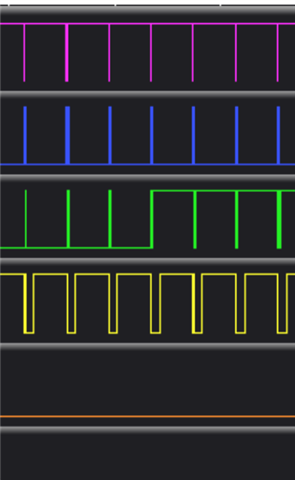

如下图,此时数据输出格式仍是正确的(通道0:DRDY、通道1:菊链上1st输出、通道3:菊链上2st输出、通道3:菊链上3st输出)

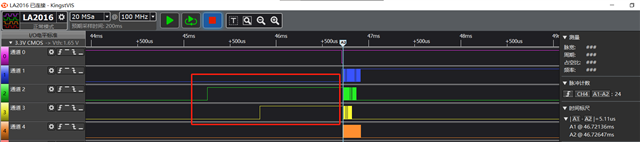

这个DOUT反转高电平的保持时间会越来越小,当小到一定程度时该芯片输出的状态位被挤掉,芯片输出数据乱码,如下图所示。

(跳变前后大约十组数据都是错误的)

(跳变前后大约十组数据都是错误的)

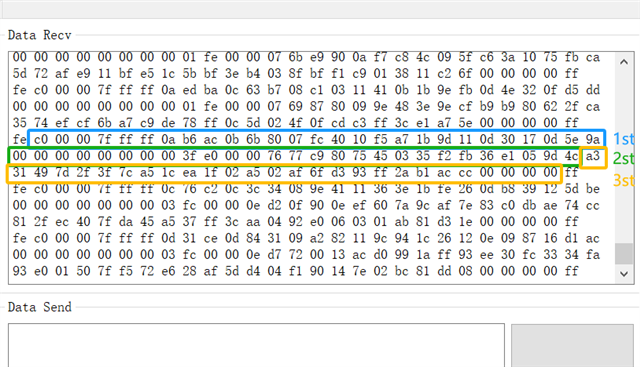

具体如下图所示,第2片状态位丢失

对应的串口读出也乱码

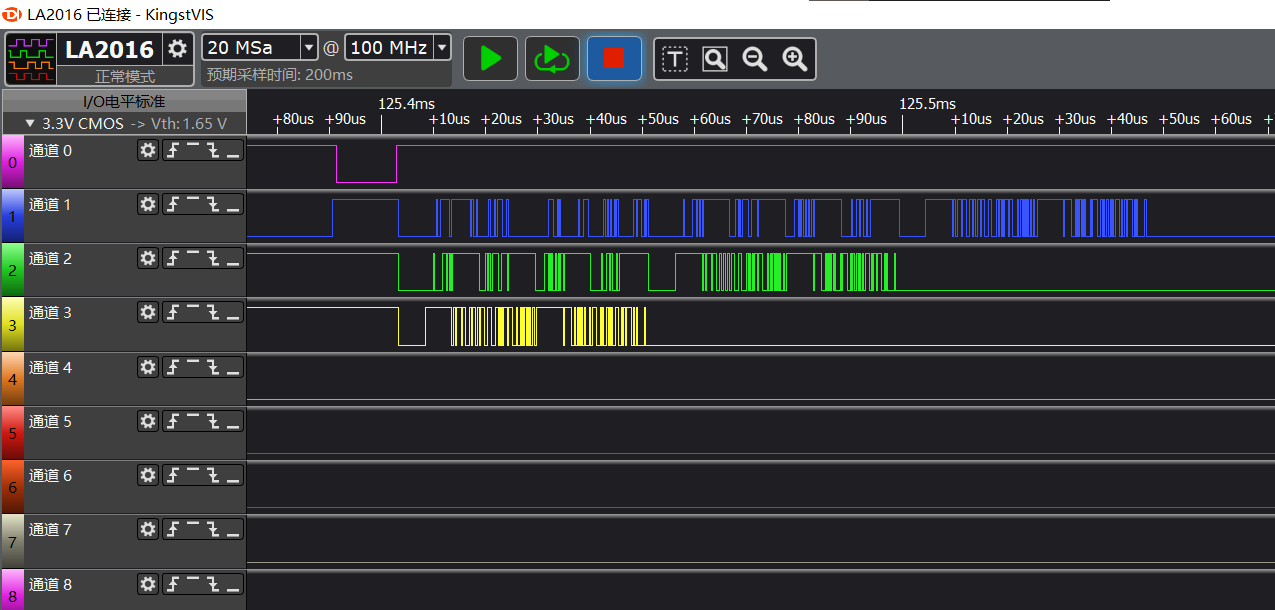

但是1st的芯片输出非常稳定(即前八个通道)DOUT输出完成一组后的电平翻转占空比始终固定,保持时间约为12uS左右,与DRDY变化保持一致。

所以是什么导致的菊链串联的后面几片的数据输出异常?

所有片使用同一外部时钟2.048MHz,此时SPI_CLK为9MHz。