Part Number: ADS9234R

请问一下,ADS9234R这个AD的寄存器如何配置,需要用到哪几个引脚?时序是怎样的?与复位信号有什么关系?感觉官方文档对寄存器配置这一块描述比较少,我用FPGA与ADS9234R做接口,写入寄出器参数,读出总是不对。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,ADS9234R的通信接口兼容的是Enhanced-SPI协议,时序可以参考Figure 49, Figure 50, Figure 51,和 Figure 52的时序图。参考7.6.2 Data Transfer Protocols的数据传输协议

与复位信号有什么关系

上电后等电压起来将复位信号拉高,默认支持的是SPI-00-S协议。

或者通过配置寄存器PROTOCOL_CFG bit6-4 改变其他模式的SPI协议。

但是读出数据与写入数据不同,而且读出数据明显不对,读寄存器时序是参考Figure 47,而且,寄存器访问过程中,convst,rdy等信号在配置寄存器过程中怎么用

CS和CONVST引脚没有接在一起吧?建议不要接在一起,单独控制。

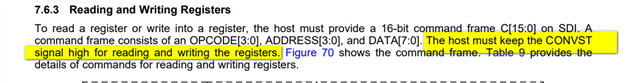

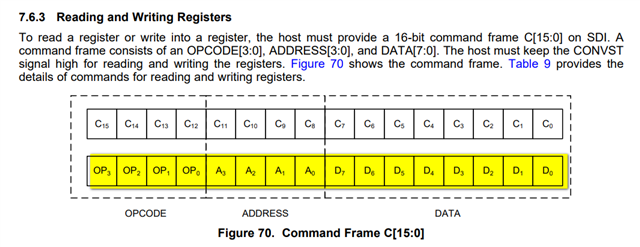

读写寄存器的时候需要将CONVST拉高。

您好,读写寄存器的时候CONVST置高电平没问题。

读写命令如下,一共16bit包含OP3~OP0,A3~A0以及8bit data。是否按照这个命令读写的?

读写是参照7.6.3的格式来访问寄存器的,写入寄存器的数据分别为X"1100"; X"1210"; X"1303; X"1400"; X"1501" ; X"1600"; X"1701";上图ila的截图中wr_data就是写入寄存器的16位数据; 读操作时,发送到SDI线上的数据为X"2100"; X"2200"; X"3200"; X"4200"; X"5200"; X"6200"; X"7200";ila的截图中rd_data就是读操作时发送到SDI上的16位数据。尝试过好多次,感觉无法正常配置ADS9234R的寄存器。目前用默认寄存器配置,能够正常采集AD数据。我使用过很多款TI和ADI的ADC,从几百K到几G赫兹的采样率的ADC,SPI配置也用过很多次,但是这个ADS9234R一直配置不成功,而且文档中配置方面的说明确实太少。

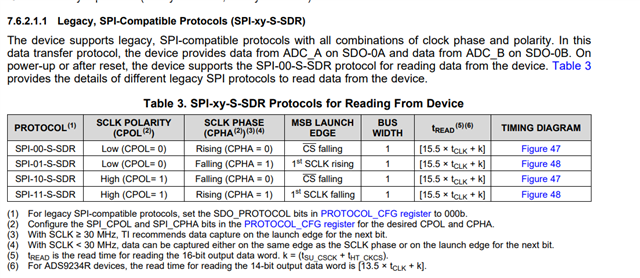

明白您的意思,这颗ADC数据手册说的是兼容的enhanced SPI协议,上电初始化后默认的是SPI-00-S 协议。

读取数据时需要通过PROTOCOL_CFG寄存器配置兼容的协议。

并且不同的协议遵循的时序要求是不一样的。参考Table3所示。

因为我没有找到这颗ADC的配置示例,我想您目前遇到的问题应该是PROTOCOL_CFG的协议配置和时序是不匹配的,导致配置不成功。

另外,根据Table3,我再补充下,SPI clock的相位和极性需要要满足您目前使用的主机比如MCU的要求。

参考Table3下面的备注(2)和(3)。

我看了文档,我都是按照SPI-00-S协议来访问的,我不是用MCU,用的是xilinx公司的FPGA,目前是能上电后,不更改寄存器配置,默认用SPI-00-S协议采集AD数据,SPI时钟采用50M,最大也只能达到1.6M的采样率,想提高采样率,还是必须要配置寄存器参数,配置过程中的时钟相位和极性,我都注意到了,文档我也读了好几遍,我现在需要的是有没有寄存器配置相关所需所有信号的时序图,这些信号包括,复位rst,sclk,sdi,sdo(X),convst,ready。有这些信号的时序图,我也不用去猜测各种信号的组合时序关系了。

我现在需要的是有没有寄存器配置相关所需所有信号的时序图,这些信号包括,复位rst,sclk,sdi,sdo(X),convst,ready。有这些信号的时序图,我也不用去猜测各种信号的组合时序关系了

您好,reset的时序比较简单,只关系到上电掉电,低有效,那么正常工作时置高就可以了。

您说的其他几个引脚的时序 ,其实在Page9的6.8 Timing Requirements也都给出了。

并且Figure 1和Figure 2给出了Zone1 Zone2传输时的数据转换和控制时序。