Part Number: ADC3683EVM

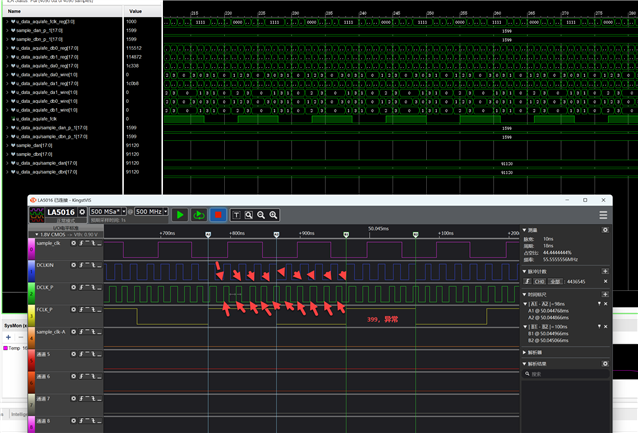

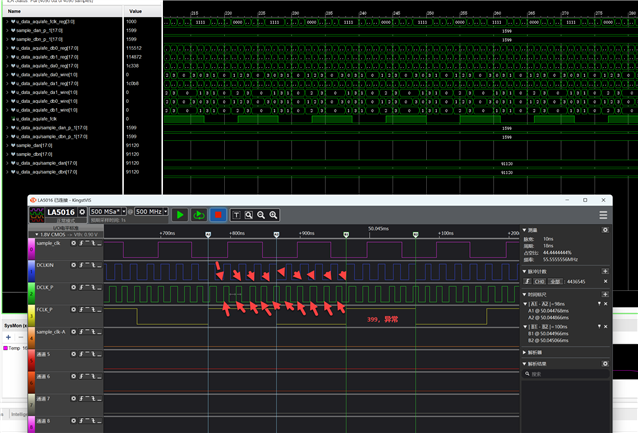

ADC3683EVM 在XILINX FPGA 开发板上,在ADC35XX GUI设定不同Test Pattern值,ADC反馈的DCLK频率是动态变化的?请老师指导下怎么调试。

如图,

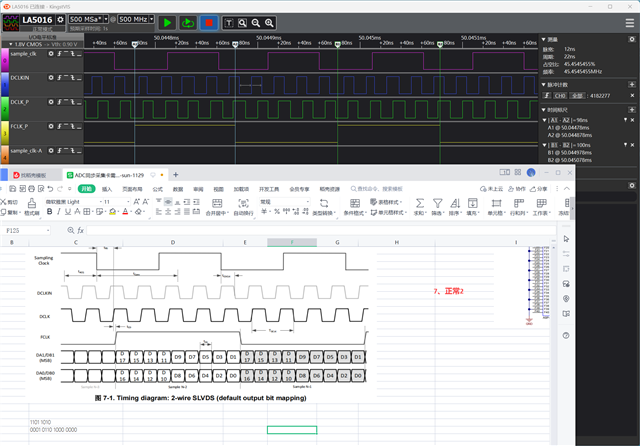

正常状态:反馈DCLK=4.5*sample_clk

异常状态:反馈DCLK=6*sample_clk

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADC3683EVM

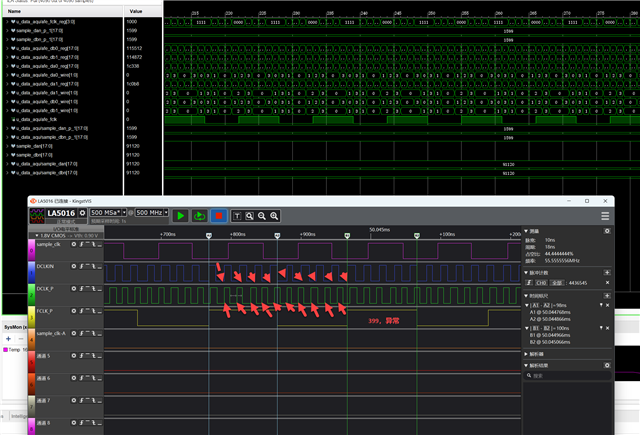

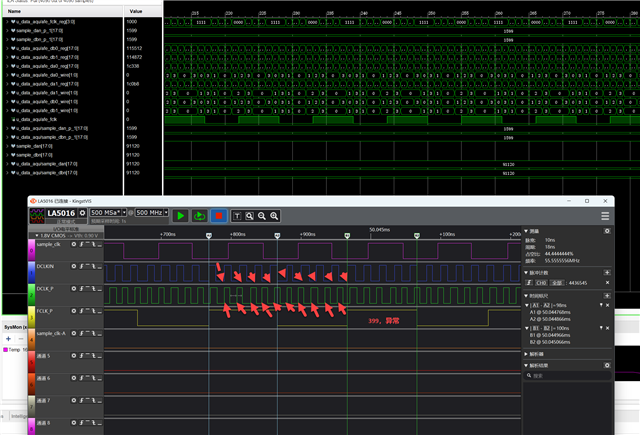

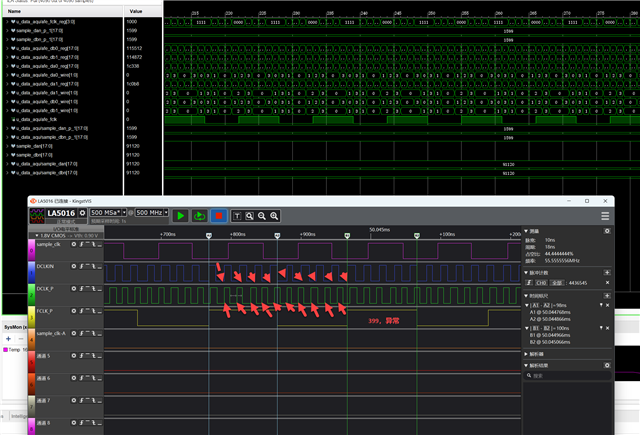

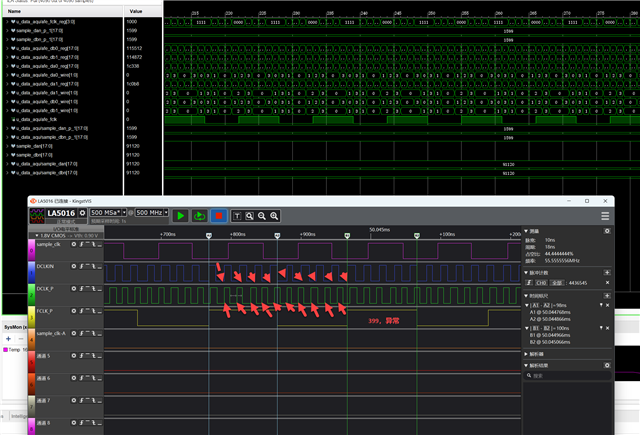

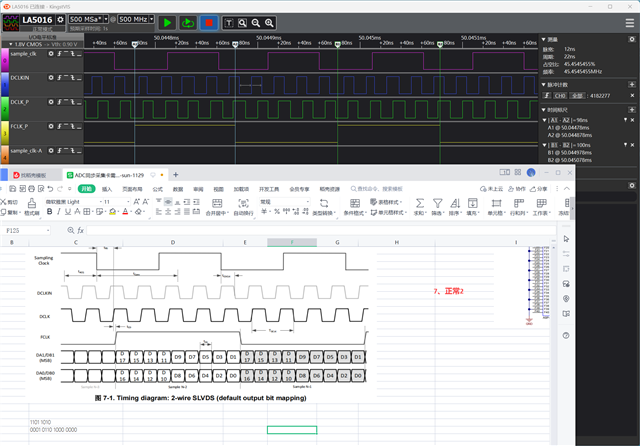

ADC3683EVM 在XILINX FPGA 开发板上,在ADC35XX GUI设定不同Test Pattern值,ADC反馈的DCLK频率是动态变化的?请老师指导下怎么调试。

如图,

正常状态:反馈DCLK=4.5*sample_clk

异常状态:反馈DCLK=6*sample_clk