Part Number: ADC3663

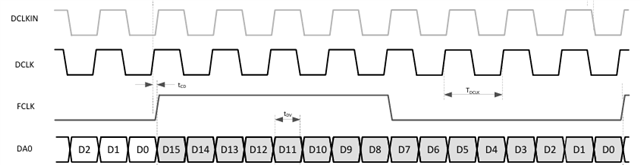

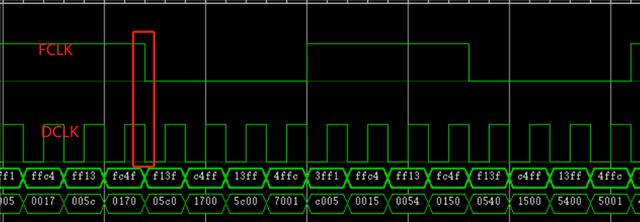

ADC3663在20Mhz的sample clock下,数据读取正常,但在40Mhz时,数据读取出现错位现象,从手册上看,正常情况下FCLK的边沿对应DCLK的上升沿,但出现问题时,FCLK的跳变沿对应的却是DCLK的下降沿,如下图所示:

问题:

DCLKin和FCLK、DCLK的逻辑输出机制上怎样的?

FPGA的控制逻辑怎样能很好的避免这种现象?

这种现象可能是什么原因导致的?硬件上的相位滞后吗还是软件的控制逻辑?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.