Part Number: ADS5282

hello,您好!

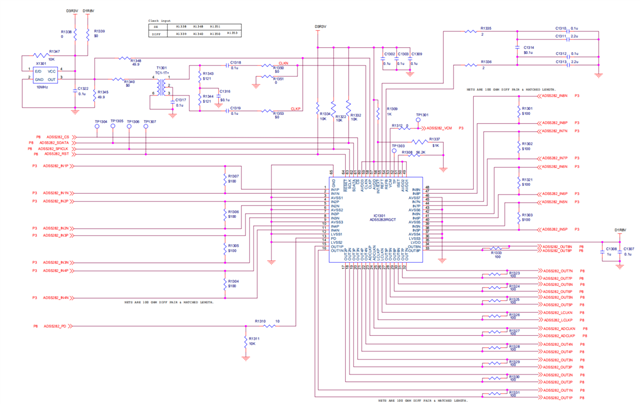

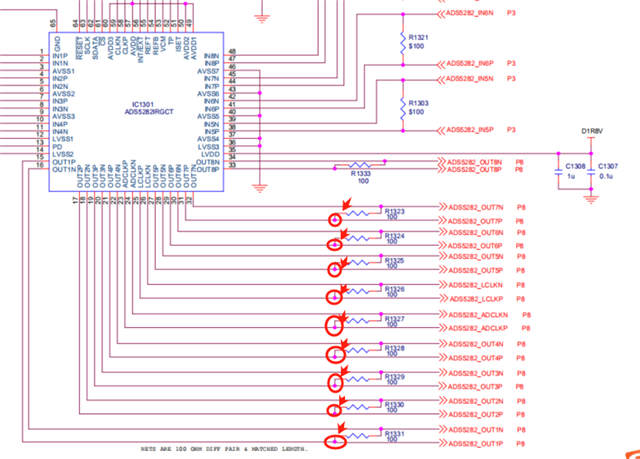

目前,我正在做一个ADC芯片与FPGA LVDS接口项目,我通过SPI接口把ADC芯片配置成LVDS TEST PATTERNS ,Set using PAT_SYNC, the normal ADC word is replaced by a fixed 111111000000 word.

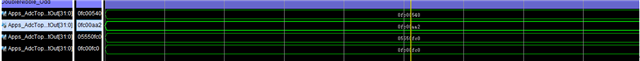

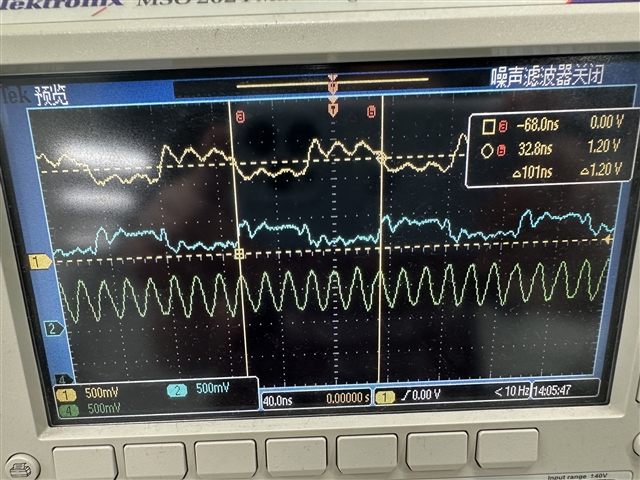

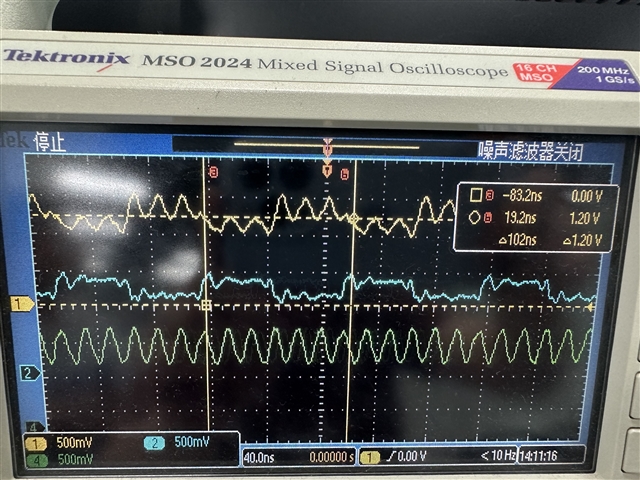

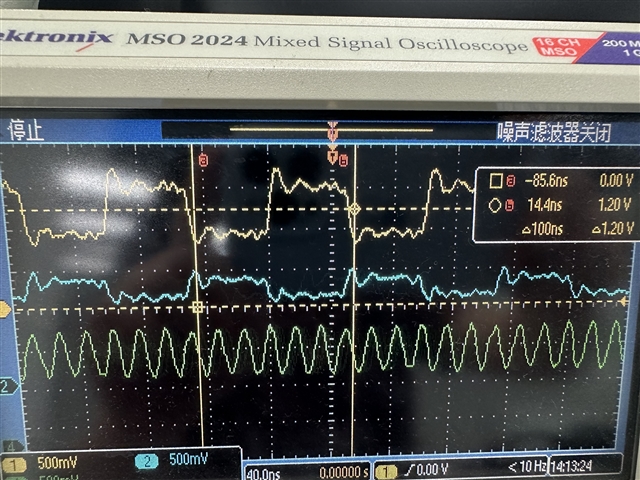

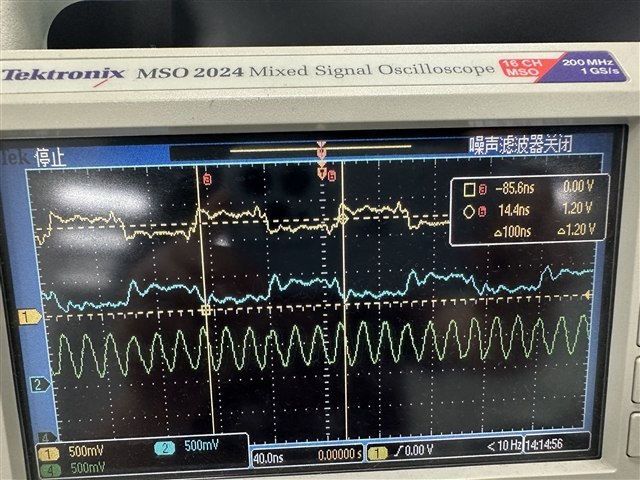

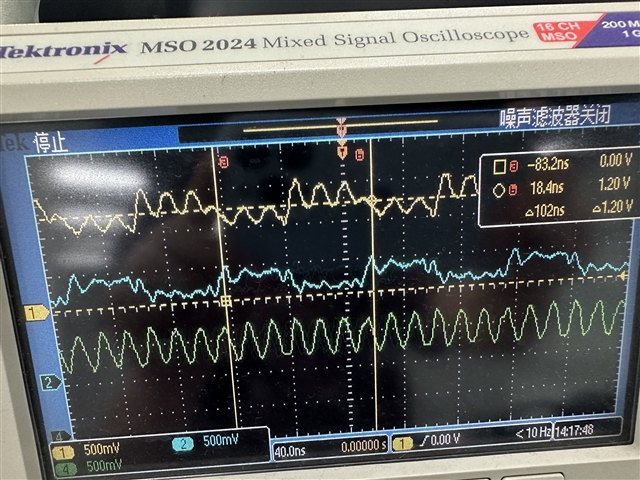

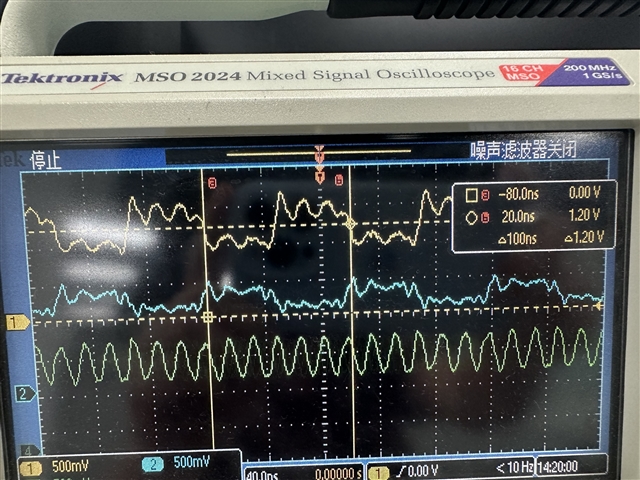

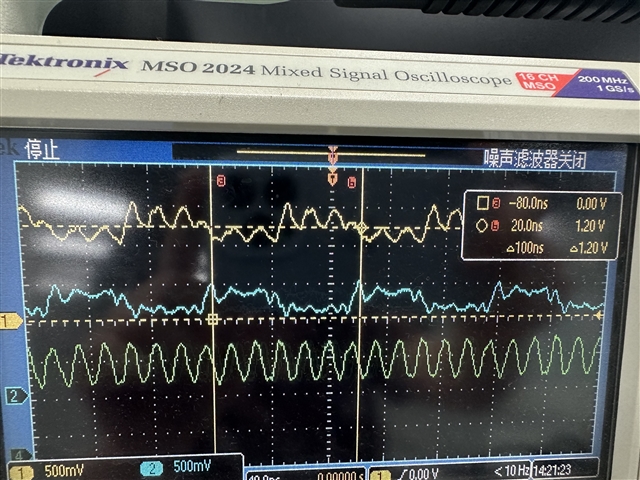

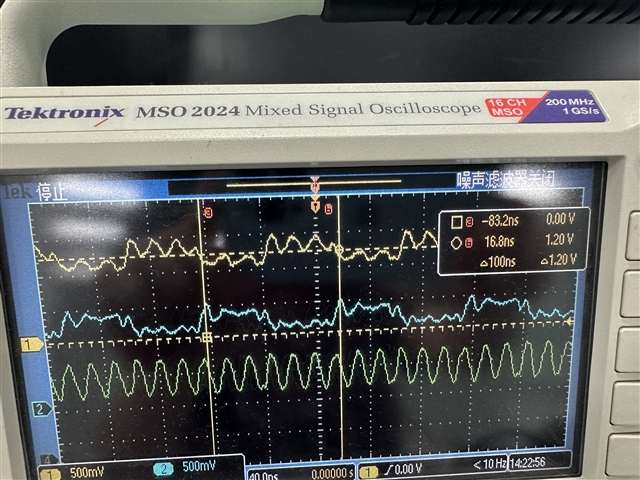

通过示波器观察ADC芯片输出的八通道数据以及随路时钟(只测试P端),LVDS bit clock <LCLKp和LCLKn>频率为60Mhz LVDS frame clock <ADCLKp和ADCLKn>频率为10Mhz

下面是八个通道的波形图:最上面波形为P端数据、中间波形为帧时钟P端、最下面波形是位时钟P端

通道一:

通道二:

通道三:

通道四:

通道五:

通道六:

通道七:

通道八:

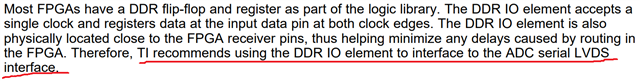

以上输出的LVDS数据与时钟正不正确?另外,如何去精准测量LVDS信号?来去确认ADC输出的数据和时钟没有问题。目前我用FPGA板子去接受八个通道数据其显示通道一、通道三、通道六数据跟ADC所发的111111000000不一致

目前,我没有能发现问题出现在那里,请求您的指导,不胜感激!