Part Number: DAC38J82

您好

我在使用贵司的一款 DAC38J82IAAVR该芯片的过程中遇到以下问题,请求贵司的支持。谢谢

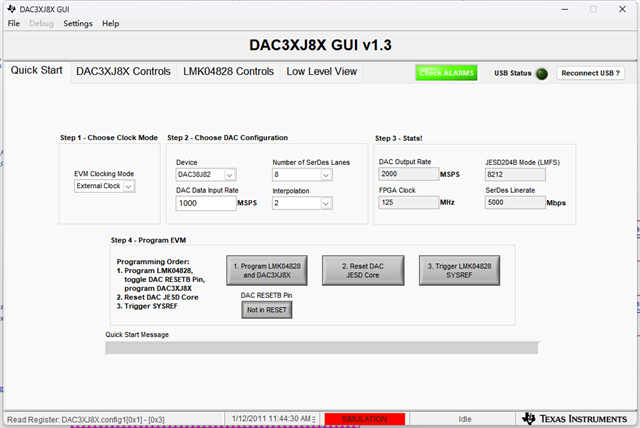

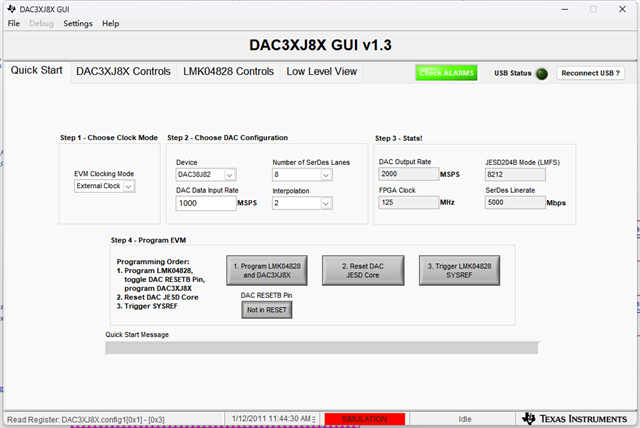

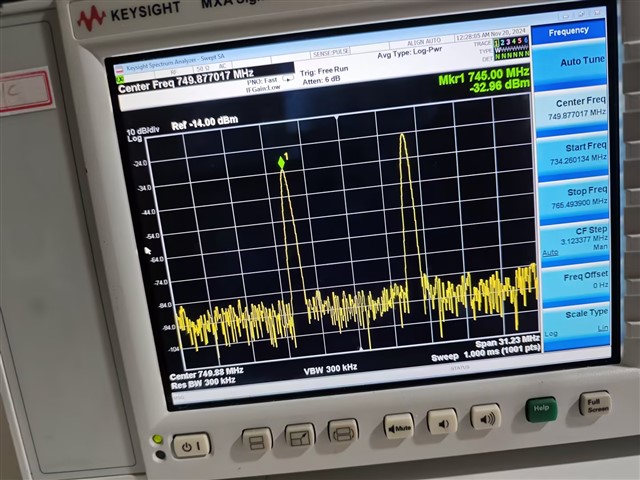

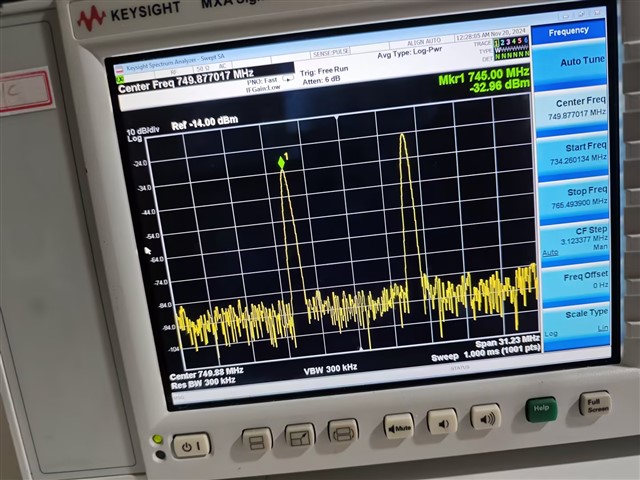

目前我的采样率为1G,2倍插值模式到2G采样;模式使用NCO 模式 NCO设置为750M 基带信号为5M;但是输出的信号出现以下的问题; 我在使用中 0x if 配置未9982 一段时间后设置为9980 , 02 寄存器配置为 2052 ,问题比较紧急 希望 请提供相关帮助,或者参考相关配置;谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DAC38J82

您好

我在使用贵司的一款 DAC38J82IAAVR该芯片的过程中遇到以下问题,请求贵司的支持。谢谢

目前我的采样率为1G,2倍插值模式到2G采样;模式使用NCO 模式 NCO设置为750M 基带信号为5M;但是输出的信号出现以下的问题; 我在使用中 0x if 配置未9982 一段时间后设置为9980 , 02 寄存器配置为 2052 ,问题比较紧急 希望 请提供相关帮助,或者参考相关配置;谢谢

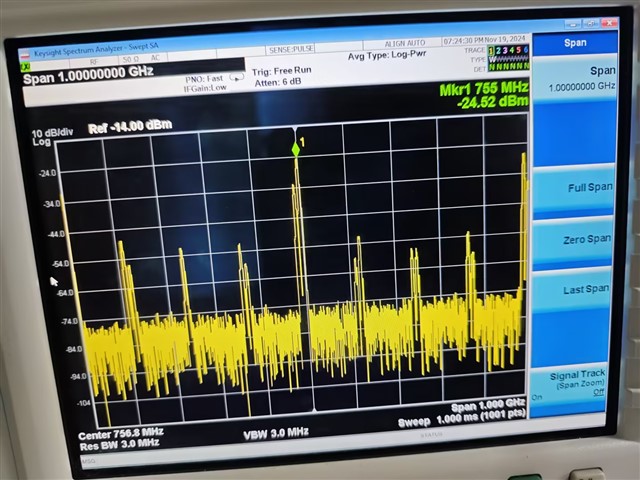

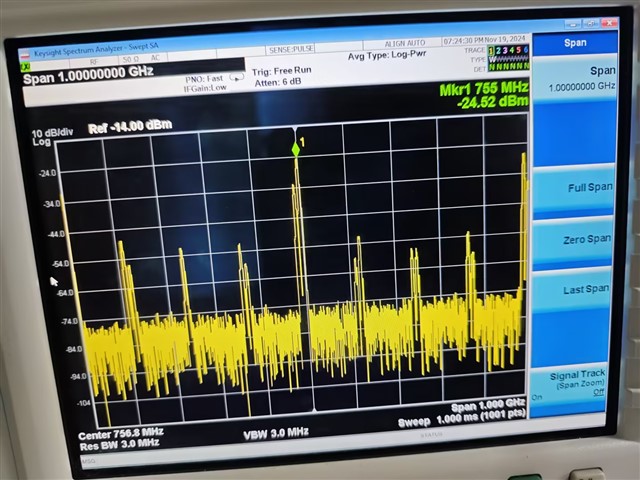

好的,我是用的DAC38J82的配置,目前使用1G采样,2倍插值,在不使用NCO时可以正常输出基带信号,后续在配置原始的NCO值为750M;在使用中会根据需要更新NCO,寄存器的配置上面:修改了配置02寄存器为2052,使能NCO,配置0x1F寄存器为9982,延时后配置未9980,我的基带信号为5M,但我DAC 输出信号如上图问题所示,span 1G;我想要达到的效果为,输出信号为755M,但现在出现了我不需要的一些频点,DAC配置如下文

DAC A与C通道输出如下图

好的,非常感谢,这是我将我目前的配置导出的情况,请查看,基本配置.cfg

或者您可以给一版参考寄存器配置,我同步尝试验证是否是寄存器配置问题导致;谢谢

DAC3XJ8X

0x00 0x0118

0x01 0x0003

0x02 0x2052

0x03 0xF301

0x04 0xFFFF

0x05 0xFF02

0x06 0xFFFF

0x07 0x3100

0x08 0x0000

0x09 0x0000

0x0A 0x0000

0x0B 0x0000

0x0C 0x0400

0x0D 0x0400

0x0E 0x0400

0x0F 0x0400

0x10 0x0000

0x11 0x0000

0x12 0x0000

0x13 0x0000

0x14 0x0000

0x15 0x0000

0x16 0x6000

0x17 0x0000

0x18 0x0000

0x19 0x6000

0x1A 0x0000

0x1B 0x0000

0x1E 0x1111

0x1F 0x9980

0x20 0x0000

0x22 0x0B37

0x23 0x000A

0x24 0x0000

0x25 0x6000

0x26 0x0000

0x2D 0x0000

0x2E 0xFFFF

0x2F 0x0004

0x30 0x0000

0x31 0x6438

0x32 0x0F00

0x33 0xAD7C

0x34 0xC000

0x3B 0x3800

0x3C 0x00A0

0x3D 0x008F

0x3E 0x0128

0x3F 0x0000

0x46 0x0044

0x47 0x190A

0x48 0x31C3

0x49 0x0000

0x4A 0xFF3E

0x4B 0x1E00

0x4C 0x1F07

0x4D 0x0101

0x4E 0x0F4F

0x4F 0x1CC1

0x50 0x0000

0x51 0x00DC

0x52 0x00FF

0x53 0x0000

0x54 0x00FC

0x55 0x00FF

0x56 0x0000

0x57 0x00FF

0x58 0x00FF

0x59 0x0000

0x5A 0x00FF

0x5B 0x00FF

0x5C 0x0000

0x5E 0x0000

0x5F 0x0123

0x60 0x4567

0x61 0x0211

0x64 0x0000

0x65 0x0000

0x66 0x0000

0x67 0x0000

0x68 0x0000

0x69 0x0000

0x6A 0x0000

0x6B 0x0000

0x6C 0x0000

0x6D 0x0000

0x6E 0x0000

0x6F 0x0000

0x70 0x0000

0x71 0x0000

0x72 0x0000

0x73 0x0000

0x74 0x0000

0x75 0x0000

0x76 0x0000

0x77 0x0000

0x78 0x0000

0x79 0x0000

0x7A 0x0000

0x7B 0x0000

0x7C 0x0000

0x7D 0x0000

您好

首先,如果FPGA提供大约100MHz单正弦波的提示音,则从DAC是否输出预期提示音开始。

然后,从FPGA向DAC提供恒定的输入,并使用NCO来转移输出音调。

执行上述两个步骤将表明问题是与FPGA数据格式有关还是与NCO的设置方式有关。

请尝试从幻灯片4开始的以下步骤,输入实际DAC输出数据,而不是示例中所示的737.28MSPS。 确认100MHz的可见音后,只需将数据格式改回原始格式并取消选中恒定输入寄存器字段,NCO将以100MHz混合来自FPGA的传入数据。